Содержание

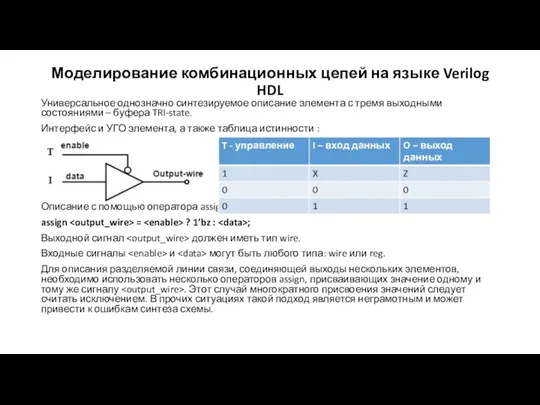

- 2. Моделирование комбинационных цепей на языке Verilog HDL Универсальное однозначно синтезируемое описание элемента с тремя выходными состояниями

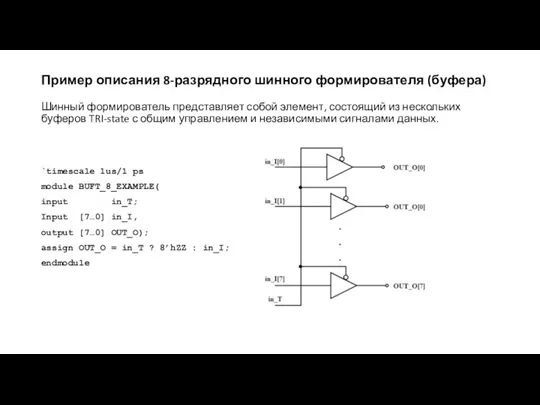

- 3. Пример описания 8-разрядного шинного формирователя (буфера) Шинный формирователь представляет собой элемент, состоящий из нескольких буферов TRI-state

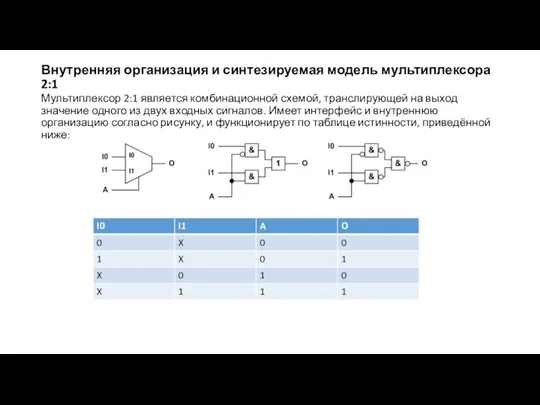

- 4. Внутренняя организация и синтезируемая модель мультиплексора 2:1 Мультиплексор 2:1 является комбинационной схемой, транслирующей на выход значение

- 5. Описание мультиплексора 2:1 с помощью оператора assign языка Verilog: assign = ? : ; Выходной сигнал

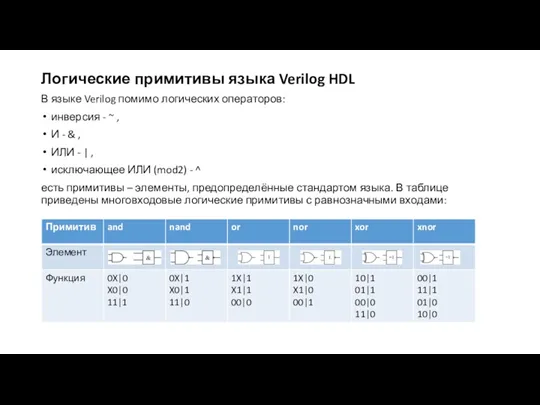

- 6. Логические примитивы языка Verilog HDL В языке Verilog помимо логических операторов: инверсия - ~ , И

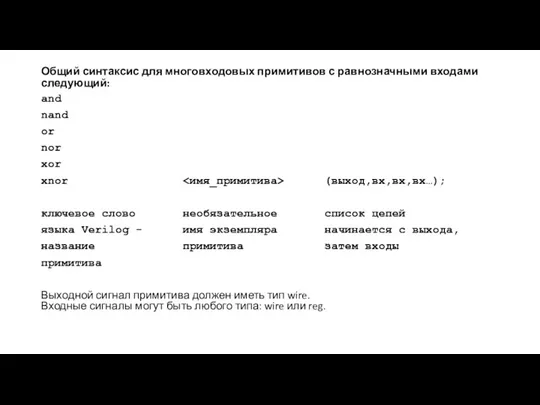

- 7. Общий синтаксис для многовходовых примитивов с равнозначными входами следующий: and nand or nor xor xnor (выход,вх,вх,вх…);

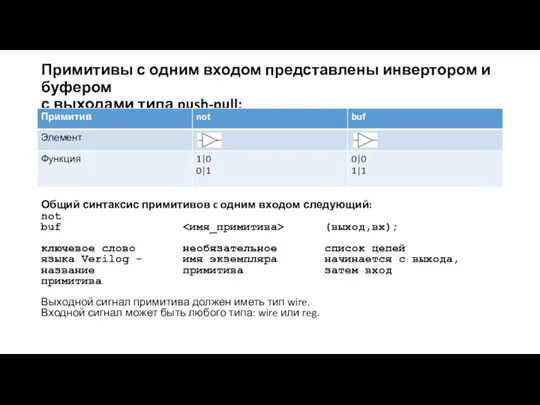

- 8. Примитивы с одним входом представлены инвертором и буфером с выходами типа push-pull: Общий синтаксис примитивов c

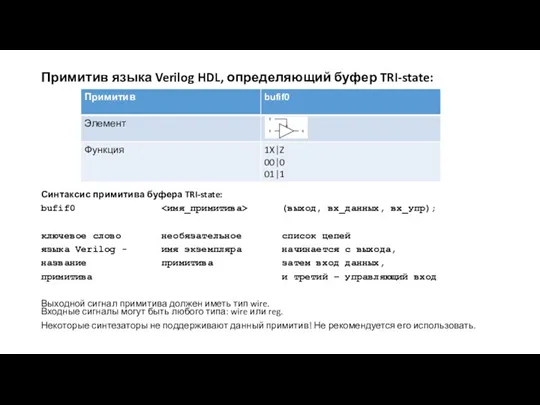

- 9. Примитив языка Verilog HDL, определяющий буфер TRI-state: Синтаксис примитива буфера TRI-state: bufif0 (выход, вх_данных, вх_упр); ключевое

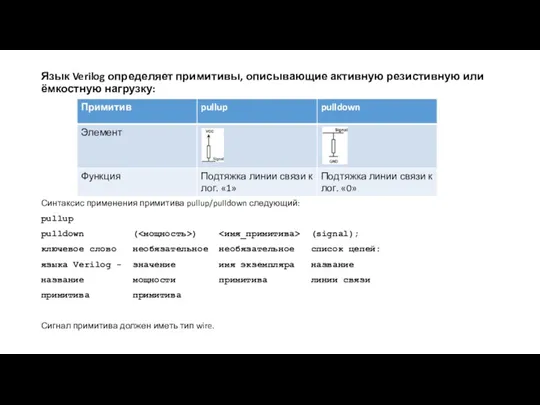

- 10. Язык Verilog определяет примитивы, описывающие активную резистивную или ёмкостную нагрузку: Синтаксис применения примитива pullup/pulldown следующий: pullup

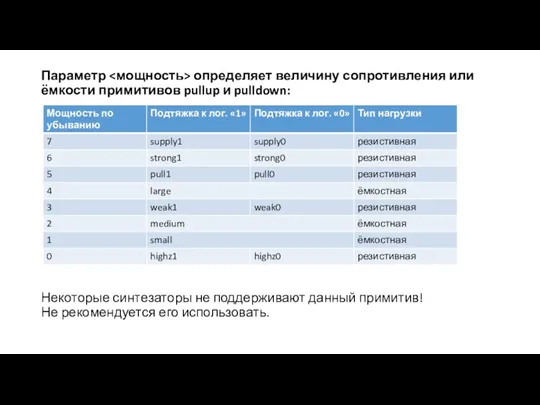

- 11. Параметр определяет величину сопротивления или ёмкости примитивов pullup и pulldown: Некоторые синтезаторы не поддерживают данный примитив!

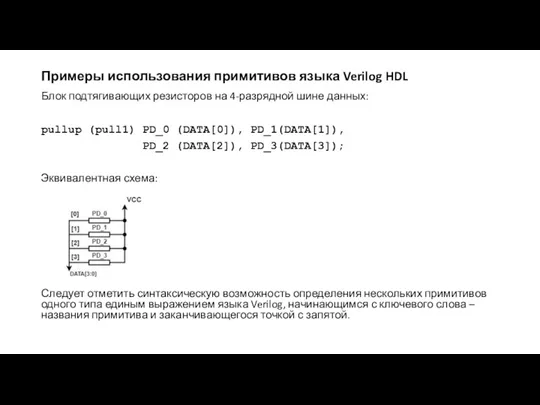

- 12. Примеры использования примитивов языка Verilog HDL Блок подтягивающих резисторов на 4-разрядной шине данных: pullup (pull1) PD_0

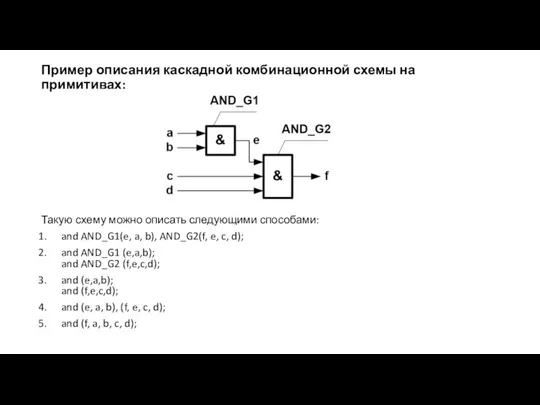

- 13. Пример описания каскадной комбинационной схемы на примитивах: Такую схему можно описать следующими способами: and AND_G1(e, a,

- 14. Классификация функциональных элементов со сложным поведением – триггеров и регистров Статические, или защёлки, или триггера с

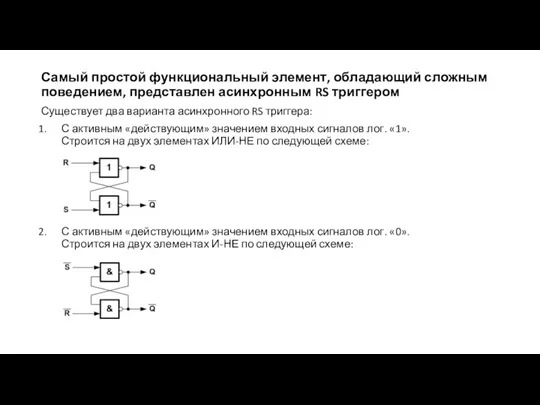

- 15. Самый простой функциональный элемент, обладающий сложным поведением, представлен асинхронным RS триггером Существует два варианта асинхронного RS

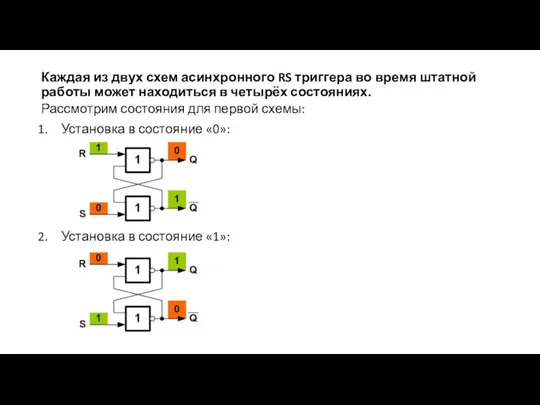

- 16. Каждая из двух схем асинхронного RS триггера во время штатной работы может находиться в четырёх состояниях.

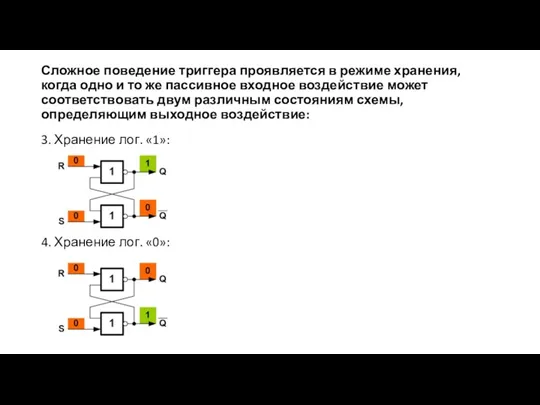

- 17. Сложное поведение триггера проявляется в режиме хранения, когда одно и то же пассивное входное воздействие может

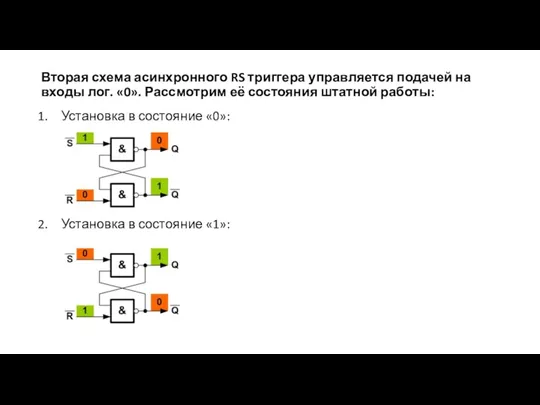

- 18. Вторая схема асинхронного RS триггера управляется подачей на входы лог. «0». Рассмотрим её состояния штатной работы:

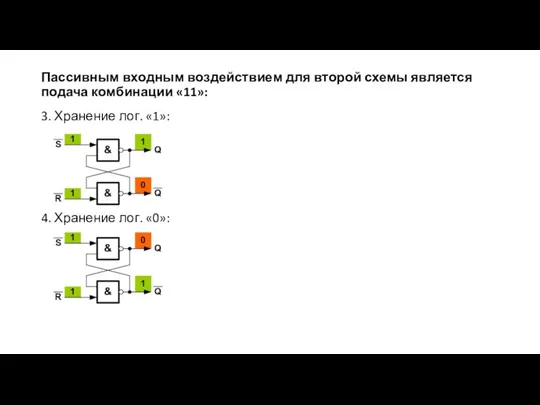

- 19. Пассивным входным воздействием для второй схемы является подача комбинации «11»: 3. Хранение лог. «1»: 4. Хранение

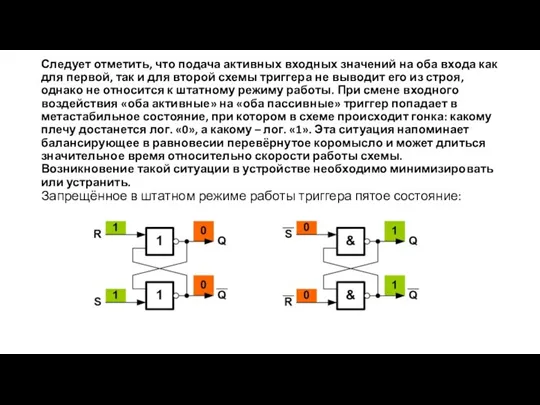

- 20. Следует отметить, что подача активных входных значений на оба входа как для первой, так и для

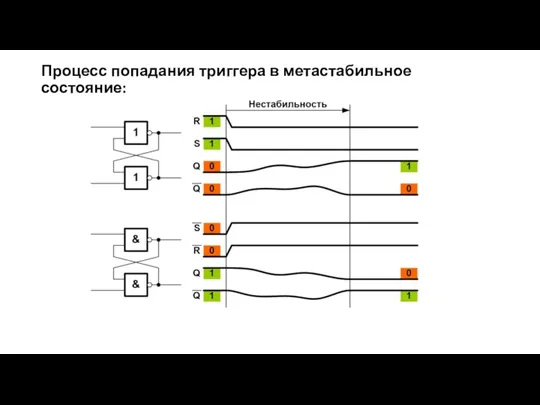

- 21. Процесс попадания триггера в метастабильное состояние:

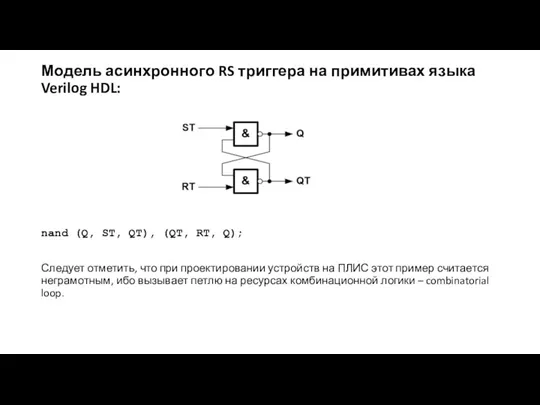

- 22. Модель асинхронного RS триггера на примитивах языка Verilog HDL: nand (Q, ST, QT), (QT, RT, Q);

- 24. Скачать презентацию

Циклы Visual Basic

Циклы Visual Basic Урок по теме Организация обмена данными

Урок по теме Организация обмена данными Обработка информации в электронных таблицах

Обработка информации в электронных таблицах Язык HTML — язык тегов

Язык HTML — язык тегов Распределение оперативной памяти ПЭВМ для программ на Pascal и С

Распределение оперативной памяти ПЭВМ для программ на Pascal и С Python. Циклы for и while

Python. Циклы for и while Аддитивные технологии

Аддитивные технологии Алгоритмы поиска. Поиск в линейных структурах

Алгоритмы поиска. Поиск в линейных структурах Электронные ресурсы для подготовки к Всероссийской олимпиаде школьников по русскому языку и литературе

Электронные ресурсы для подготовки к Всероссийской олимпиаде школьников по русскому языку и литературе Modeling and Solving Constraints. Basic Idea

Modeling and Solving Constraints. Basic Idea Программное обеспечение

Программное обеспечение Блогеры

Блогеры Технология создания и обработки графической информации

Технология создания и обработки графической информации Язык программирования Pascal. Ветвление

Язык программирования Pascal. Ветвление Педагогиканы оқытуда компьютерлік технологияларды қолдану

Педагогиканы оқытуда компьютерлік технологияларды қолдану Элемент управления ListBox. Строки в C#

Элемент управления ListBox. Строки в C# Усадьба Прекрасные зори

Усадьба Прекрасные зори Кроссворд по информатике

Кроссворд по информатике Система справочно-информационной и аналитической документации. (Тема 4)

Система справочно-информационной и аналитической документации. (Тема 4) Польза от интернета

Польза от интернета Занятие №7 Symfony, Composer, Реализация таблицы

Занятие №7 Symfony, Composer, Реализация таблицы История создания компьютера. 7 класс

История создания компьютера. 7 класс Основы информационно-библиографической культуры

Основы информационно-библиографической культуры Основы HTML. Создание сайтов в текстовом редакторе

Основы HTML. Создание сайтов в текстовом редакторе Электронные таблицы Ехсel. (Лекция 3)

Электронные таблицы Ехсel. (Лекция 3) Интерфейс и основные возможности графических редакторов

Интерфейс и основные возможности графических редакторов Файлы и файловые структуры (6 класс)

Файлы и файловые структуры (6 класс) Возможности CSS3

Возможности CSS3