Содержание

- 2. План лекции Устройство компьютера Устройство процессора Режимы работы процессора Регистры процессора Языки ассемблера Формат команд (инструкций)

- 3. Основные понятия Ассемблер – транслятор исходного кода программы, на языке ассемблера в машинный код Дизассемблер Машинный

- 4. Фон-неймановская архитектура Принцип однородности памяти Принцип адресности Принцип программного управления Принцип двоичного кодирования

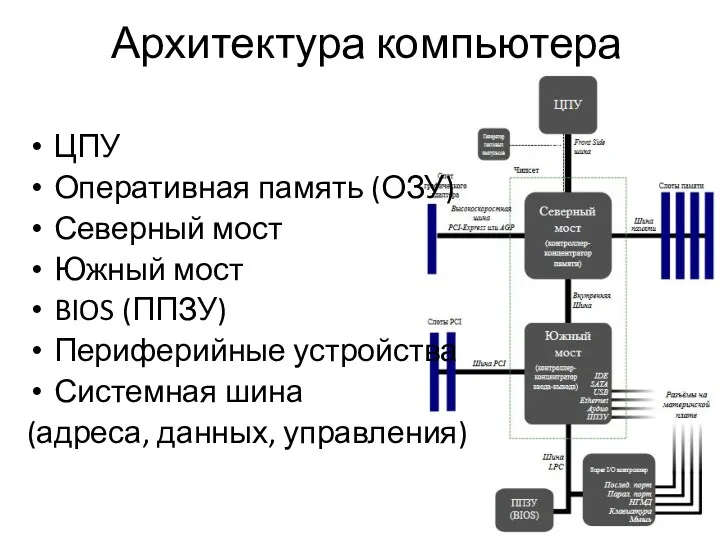

- 5. Архитектура компьютера ЦПУ Оперативная память (ОЗУ) Северный мост Южный мост BIOS (ППЗУ) Периферийные устройства Системная шина

- 6. Устройство персонального компьютера

- 7. Процессор Регистры АЛУ RSB Кэш-память (кода и данных) TLB L1, L2, L3

- 8. Материнская плата

- 9. Режимы работы процессора Реальный режим (real mode) Защищенный режим (protected mode) Режим виртуального 8086 Режим системного

- 10. Кольца защиты (Ring) Ring -2 (Режим системного управления, System Management Mode) Ring -1 (режим гипервизора, Hypervisor

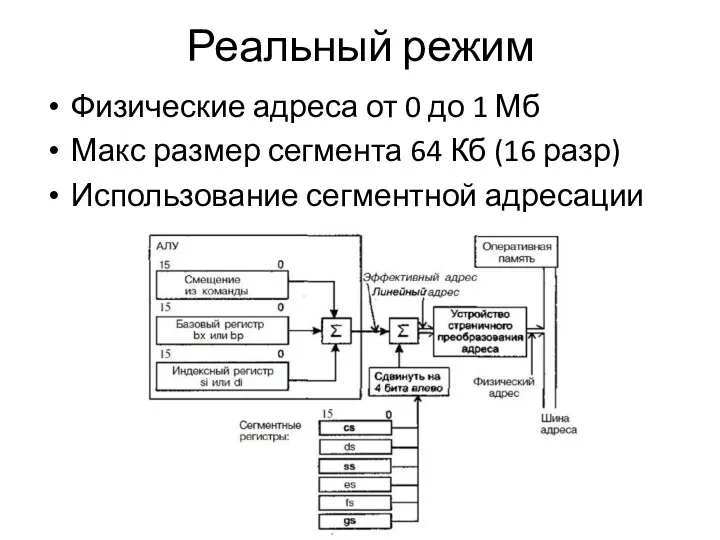

- 11. Реальный режим Физические адреса от 0 до 1 Мб Макс размер сегмента 64 Кб (16 разр)

- 12. Типы данных Двоичные числа Двоично-десятичные числа Неупакованный BCD-формат Упакованный BCD-формат Числа с плавающей точкой Символьный тип

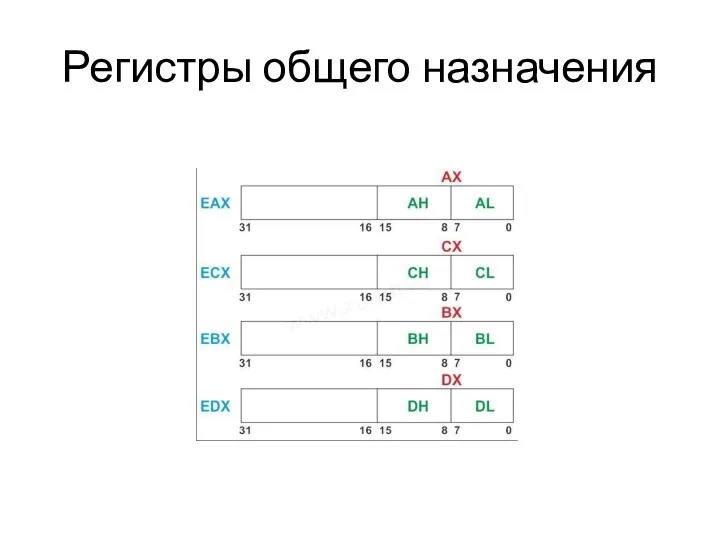

- 13. Регистры процессора Регистры общего назначения (EAX, EBX, ECX, EDX) Адресные регистры (ESI, EDI, EBP) Управляющие регистры

- 14. Регистры общего назначения

- 15. Адресные регистры ESI – индекса источника EDI - регистр индекса результата EBP - регистр указатель стековой

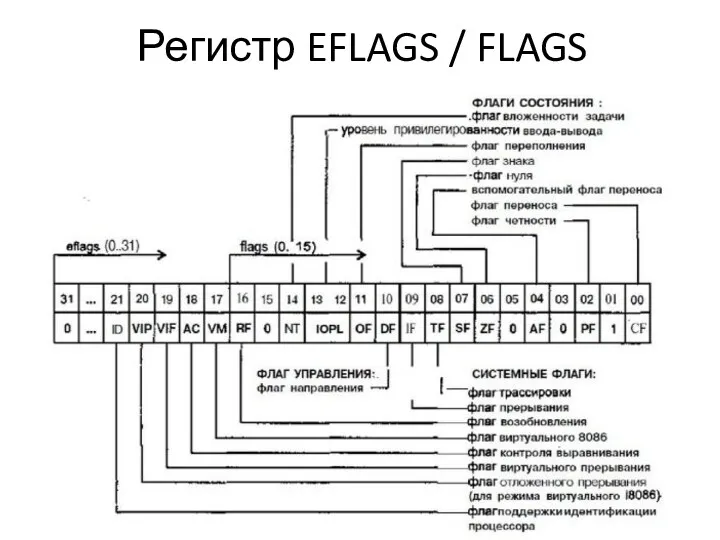

- 16. Регистры состояния ESP - Указатель на вершину стека EIP - Cчетчик команд EFLAGS - Регистр флагов

- 17. Регистры управления CR0 CR1 CR2 CR3 CR4

- 18. Регистр EFLAGS / FLAGS

- 19. Сегментные регистры 16-битные регистры для хранения селекторов сегмента CS – сегмент кода DS – сегмент данных

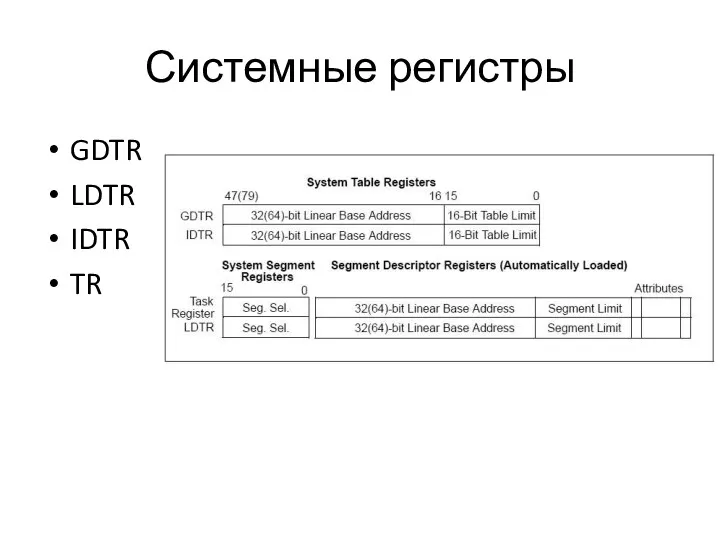

- 20. Системные регистры GDTR LDTR IDTR TR

- 21. Регистры x64

- 22. Порты ввода/вывода (I/O Ports) Используются для взаимодействия с утройствами IN eax, port_num (DX) – чтение из

- 23. MSR–регистры (Model-Specific Registers) Зависят от модели процессора Вызываются только из режима ядра RDMSR – чтение, ECX

- 24. Расширения инструкций процессора Работа с аудио- и видео-данными FPU / NPX MMX MMX Extended 3dNow! 3dNow!

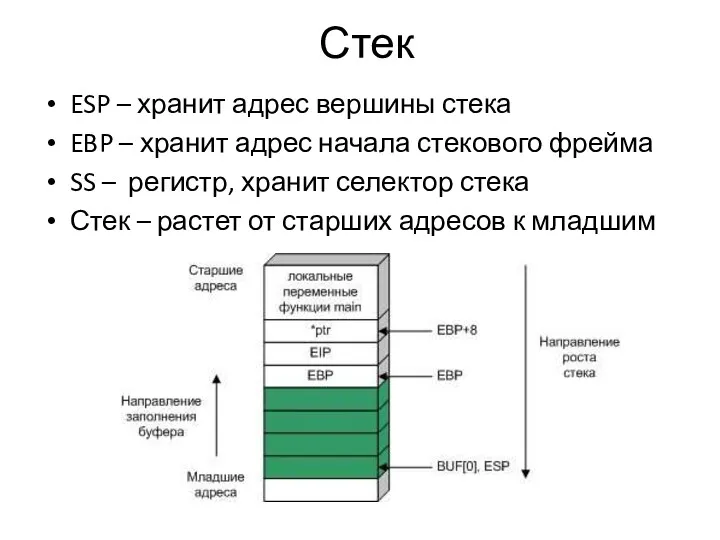

- 25. Стек ESP – хранит адрес вершины стека EBP – хранит адрес начала стекового фрейма SS –

- 26. Языки ассемблера Команды языка соответствуют инструкциям процессора Синтаксисы: Intel AT&T Ассемблеры: MASM NASM FASM TASM GAS

- 27. Типы команд Арифметические Логические Передачи данных Перехода Пропуска Вызова подпрограммы Возврата из подпрограммы Смешанные

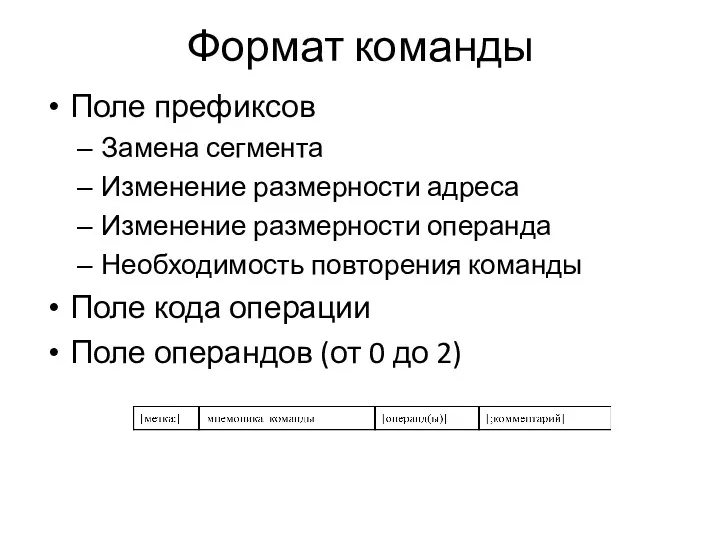

- 28. Формат команды Поле префиксов Замена сегмента Изменение размерности адреса Изменение размерности операнда Необходимость повторения команды Поле

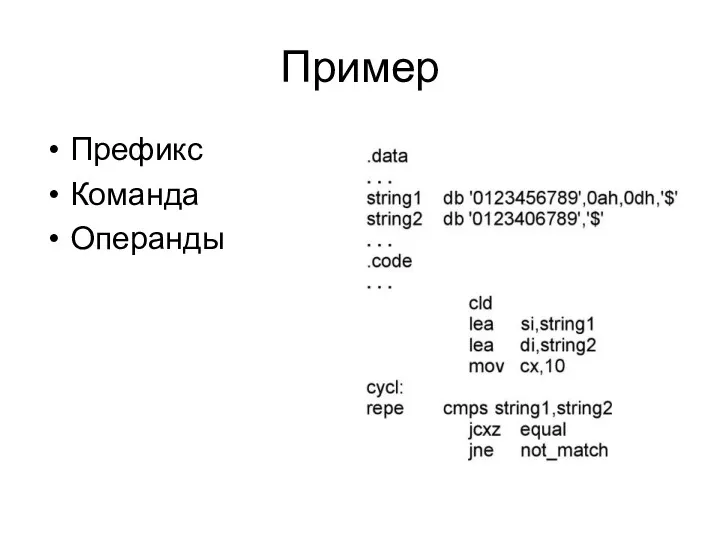

- 29. Пример Префикс Команда Операнды

- 30. Типы операндов Байт Слово Десятичный операнд Разряд Число Составной операнд

- 31. Способы адресации [1] Регистровая адресация mov ax, bx Непосредственная адресация mov ax, 2 Прямая адресация mov

- 32. Способы адресации [2] Косвенная адресация с масштабированием mov eax, [esi*3]+2 Адресация по базе с индексированием mov

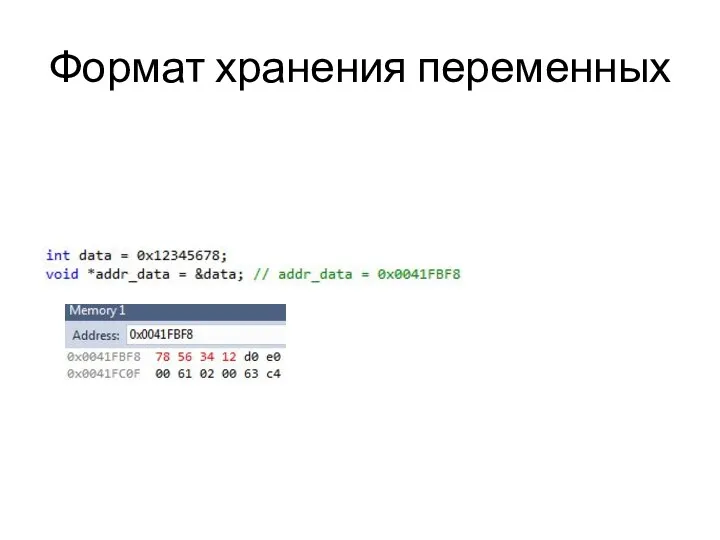

- 33. Порядок байт big-endian, от старшего к младшему (SPARC, TCP/IP) little-endian, от младшего к старшему (x86) bi-endian

- 34. Формат хранения переменных

- 35. ASCII

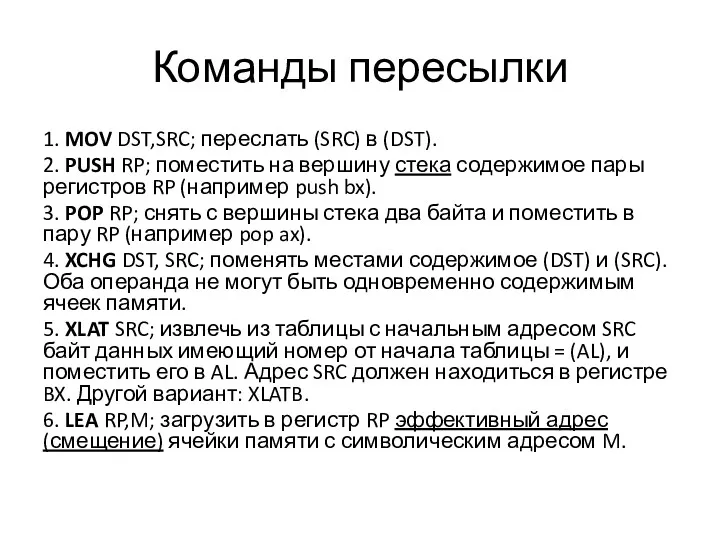

- 36. Команды пересылки 1. MOV DST,SRC; переслать (SRC) в (DST). 2. PUSH RP; поместить на вершину стека

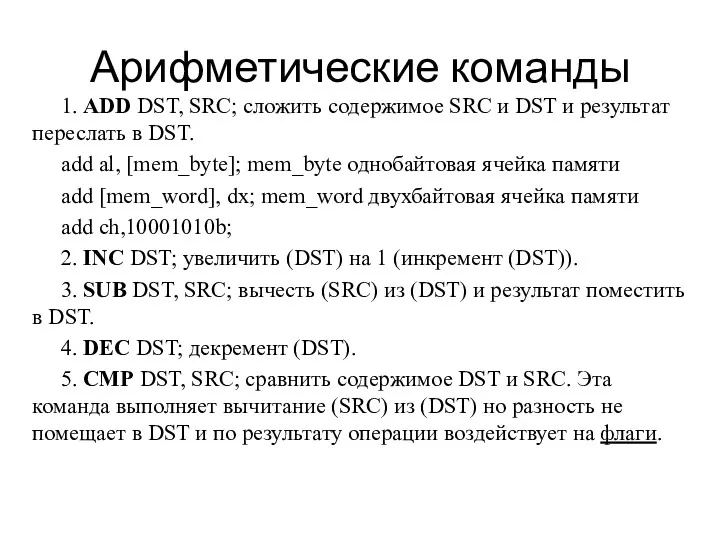

- 37. Арифметические команды 1. ADD DST, SRC; сложить содержимое SRC и DST и результат переслать в DST.

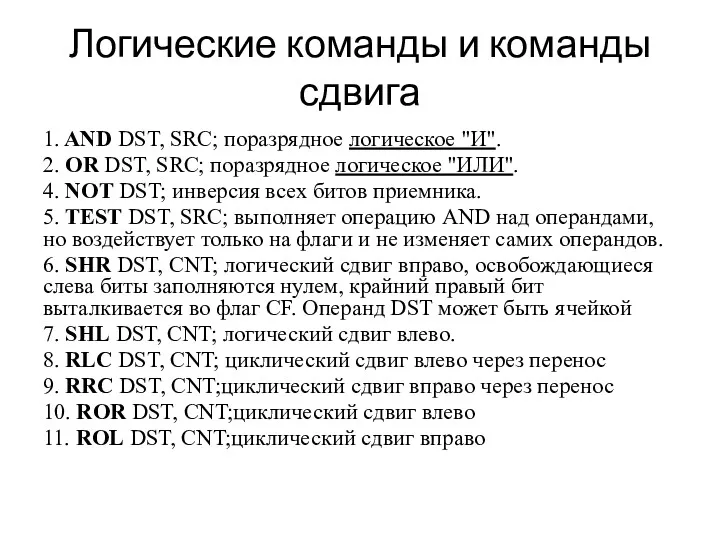

- 38. Логические команды и команды сдвига 1. AND DST, SRC; поразрядное логическое "И". 2. OR DST, SRC;

- 39. Использование сдвигов Умножение Деление Работа с 64 переменными

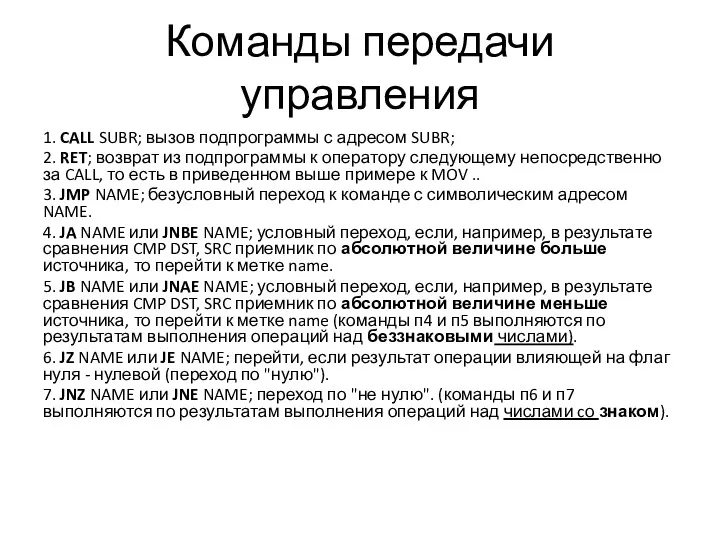

- 40. Команды передачи управления 1. CALL SUBR; вызов подпрограммы с адресом SUBR; 2. RET; возврат из подпрограммы

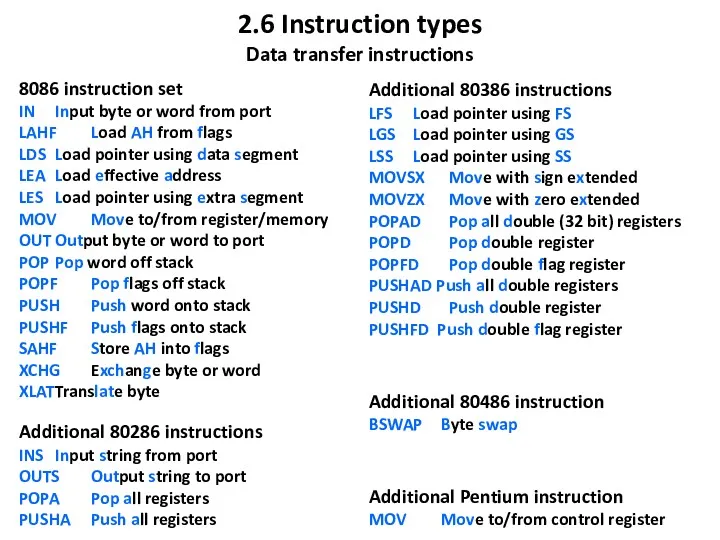

- 41. 2.6 Instruction types Data transfer instructions 8086 instruction set IN Input byte or word from port

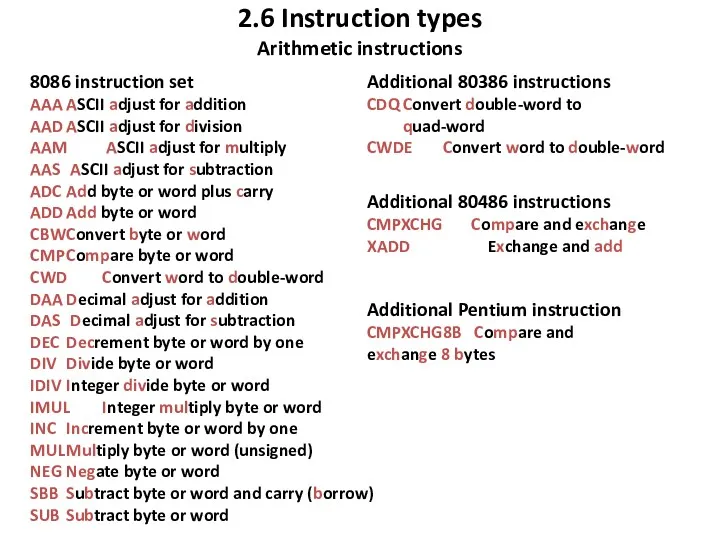

- 42. 2.6 Instruction types Arithmetic instructions 8086 instruction set AAA ASCII adjust for addition AAD ASCII adjust

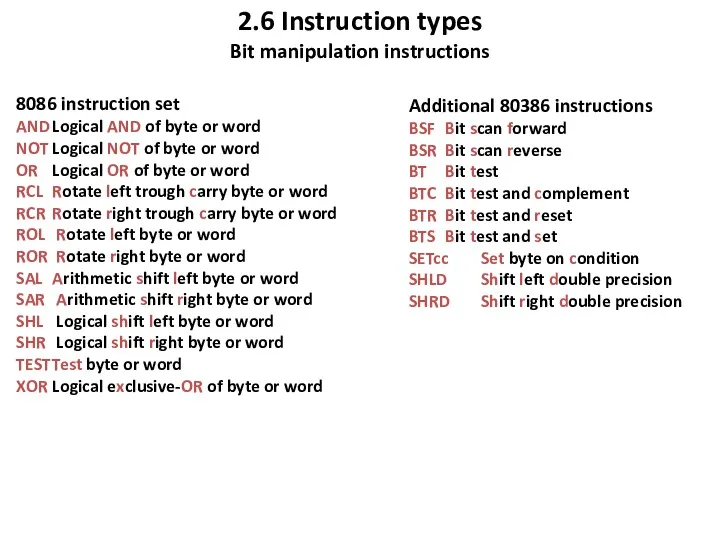

- 43. 2.6 Instruction types Bit manipulation instructions 8086 instruction set AND Logical AND of byte or word

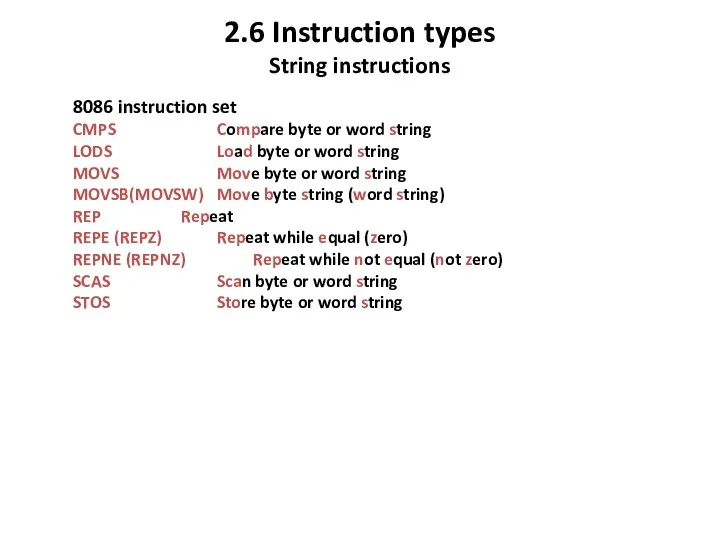

- 44. 2.6 Instruction types String instructions 8086 instruction set CMPS Compare byte or word string LODS Load

- 45. Основные команды CALL / RET JMP PUSH / POP JE / JNE XOR MOV CMP NOP

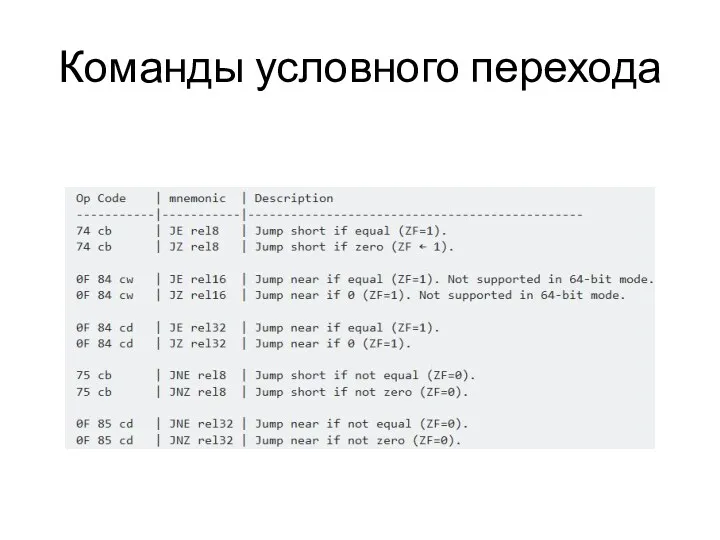

- 46. Команды условного перехода

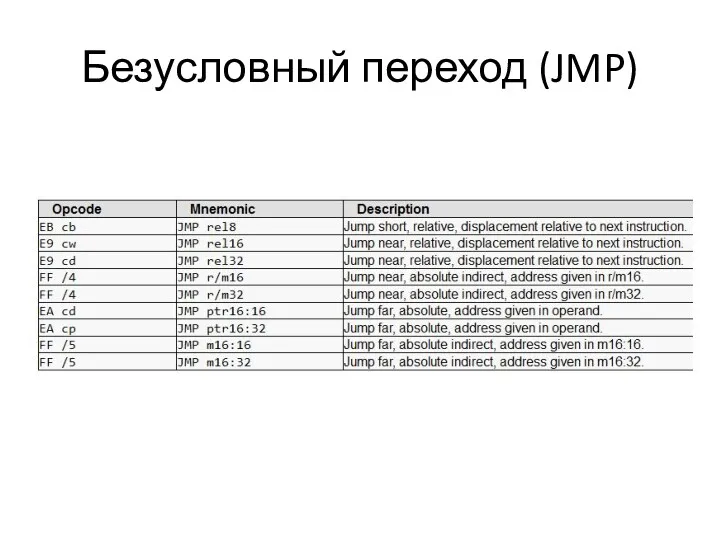

- 47. Безусловный переход (JMP)

- 48. NOP No OPeration 0x90

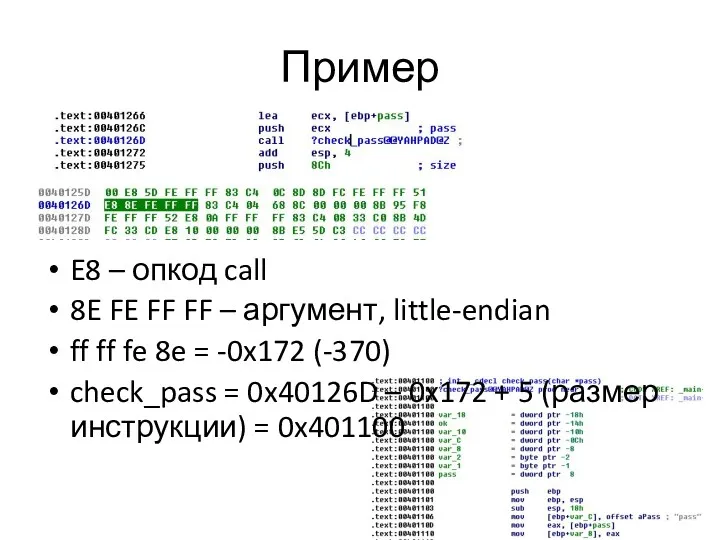

- 49. Пример E8 – опкод call 8E FE FF FF – аргумент, little-endian ff ff fe 8e

- 50. Опкоды инструкций Принцип построения

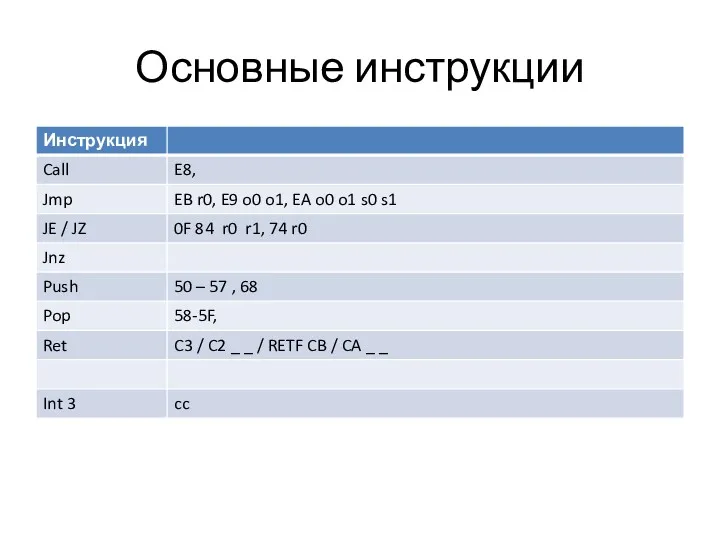

- 51. Основные инструкции

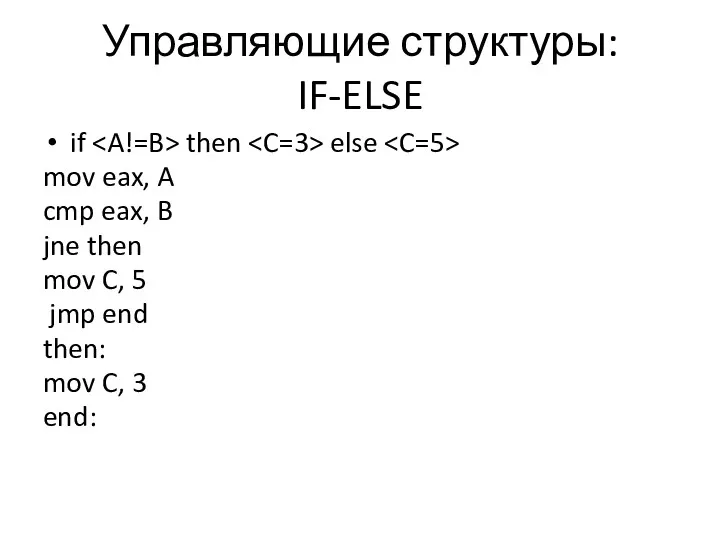

- 52. Управляющие структуры: IF-ELSE if then else mov eax, A cmp eax, B jne then mov C,

- 53. Управляющие структуры:switch-case mov eax, I shl bx, 1 jmp cs:jump_table[bx] jump_table dw foo0, foo1, foo2 foo0:

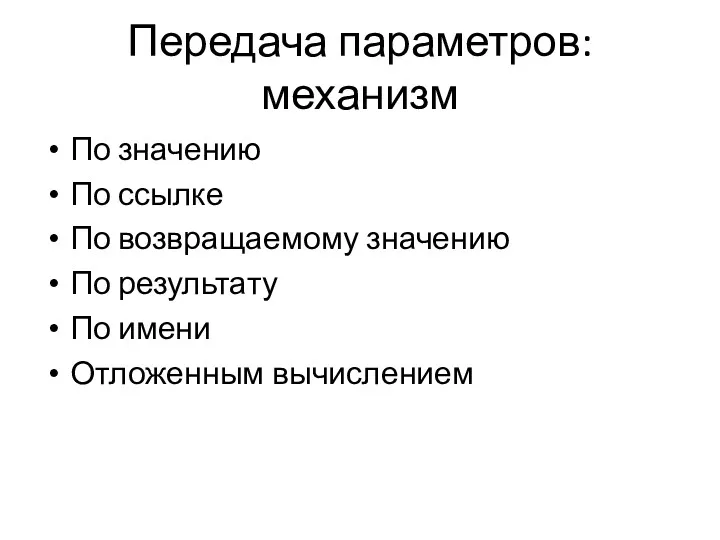

- 54. Передача параметров: механизм По значению По ссылке По возвращаемому значению По результату По имени Отложенным вычислением

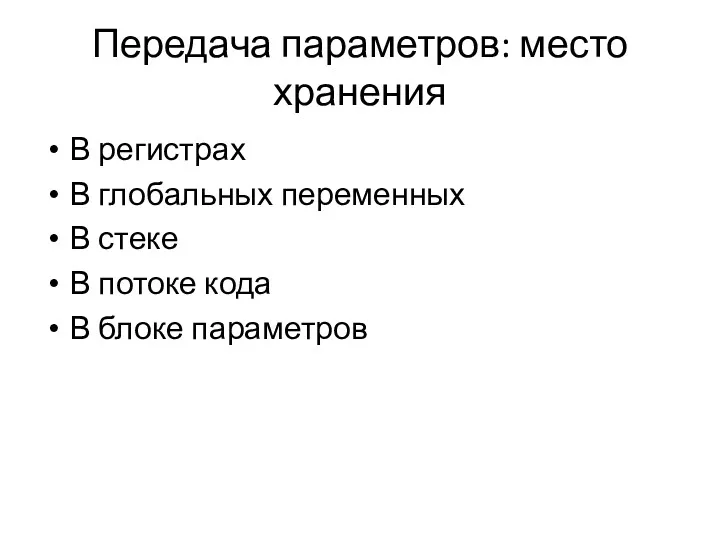

- 55. Передача параметров: место хранения В регистрах В глобальных переменных В стеке В потоке кода В блоке

- 56. Структура исполняемого файла Секции: Кода Данных Стека Кучи Неинициализированных переменных (bss)

- 57. Процесс компиляции

- 58. Средства отладки Linux: ktrace, gdb, ddd, readelf, nm

- 59. Средства разработки GCC \ CL VS

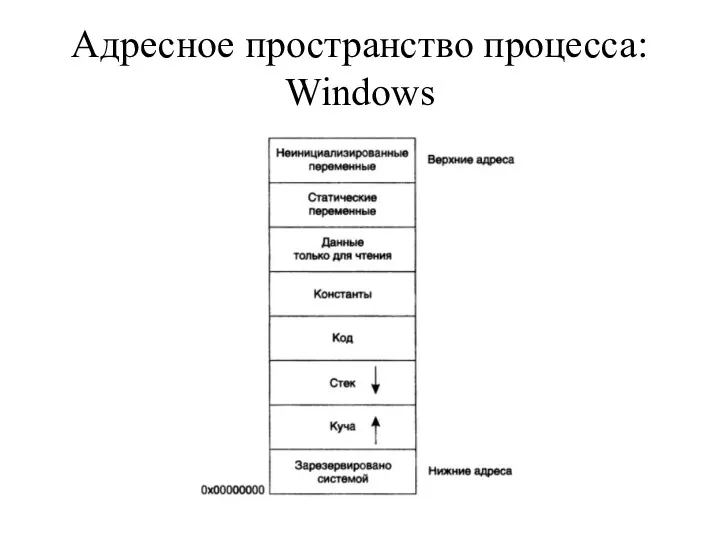

- 60. Адресное пространство процесса: Windows

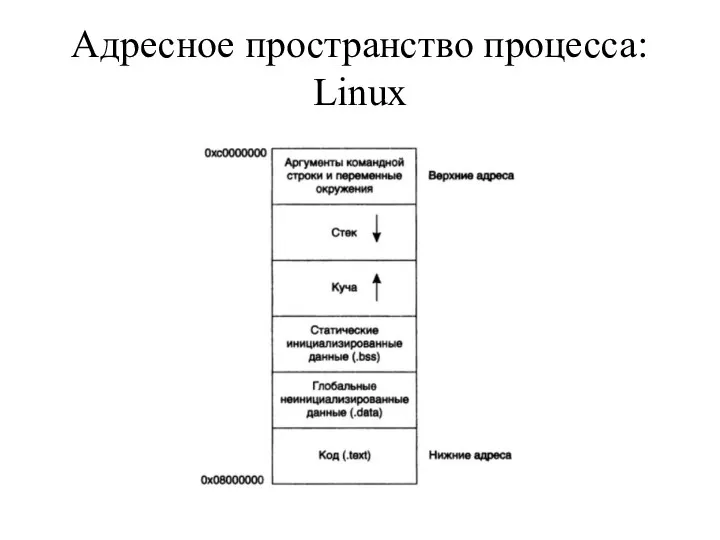

- 61. Адресное пространство процесса: Linux

- 62. Структура стека

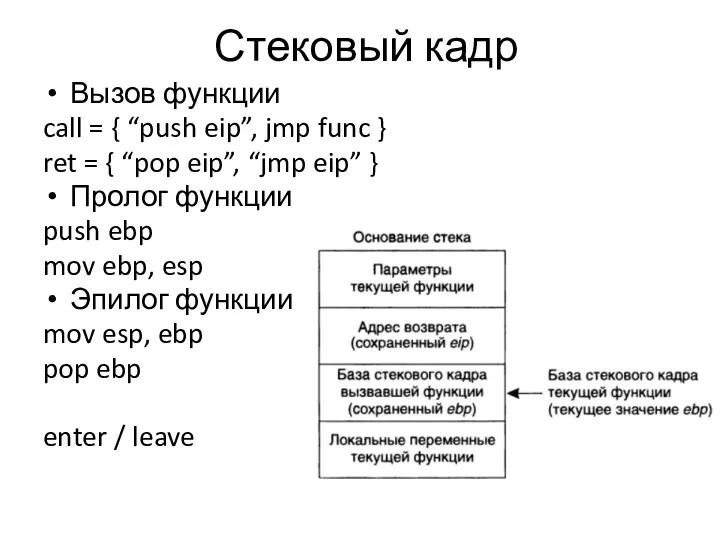

- 63. Стековый кадр Вызов функции call = { “push eip”, jmp func } ret = { “pop

- 64. Стековый кадр

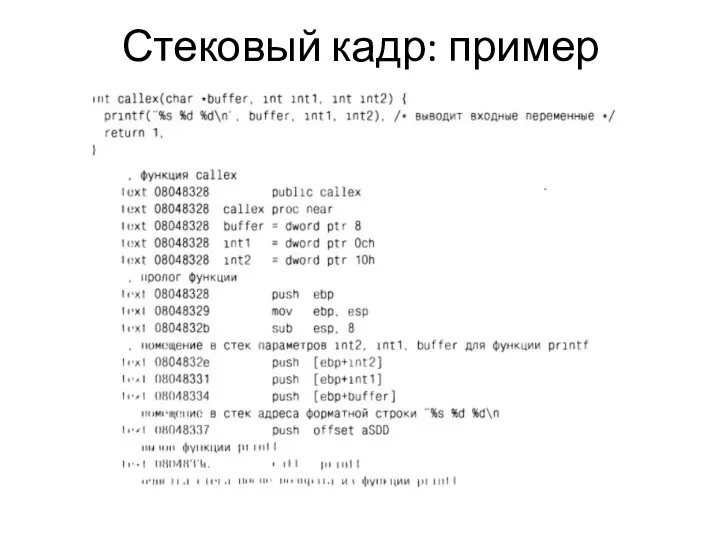

- 65. Стековый кадр: пример

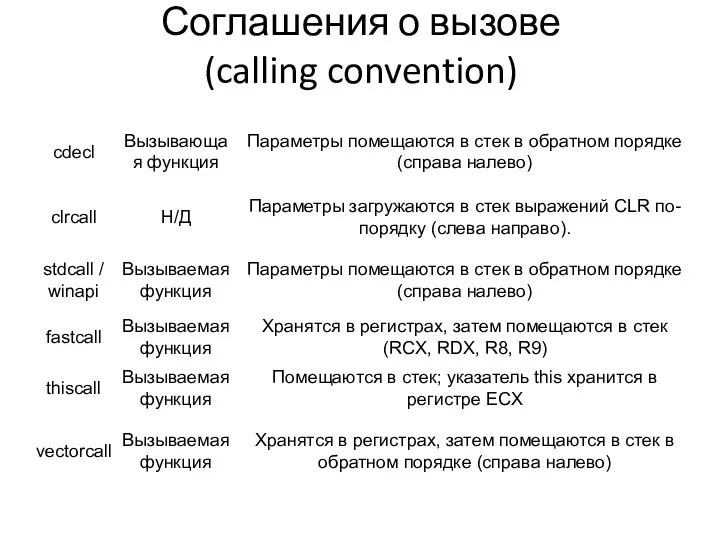

- 66. Соглашения о вызове (calling convention)

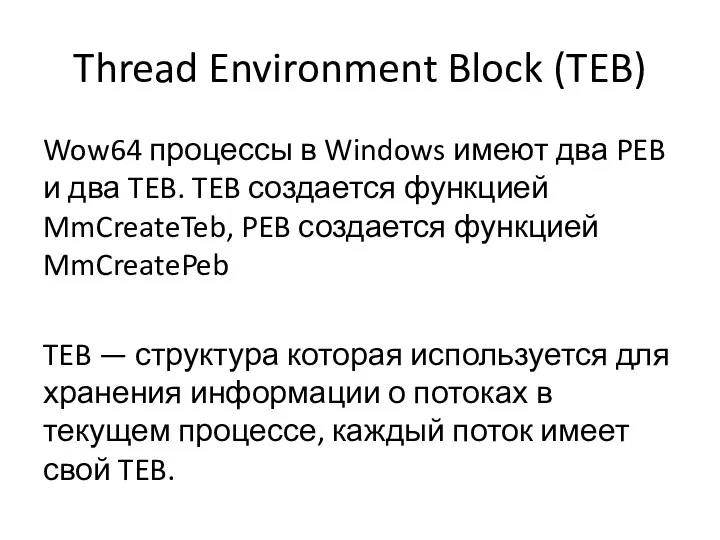

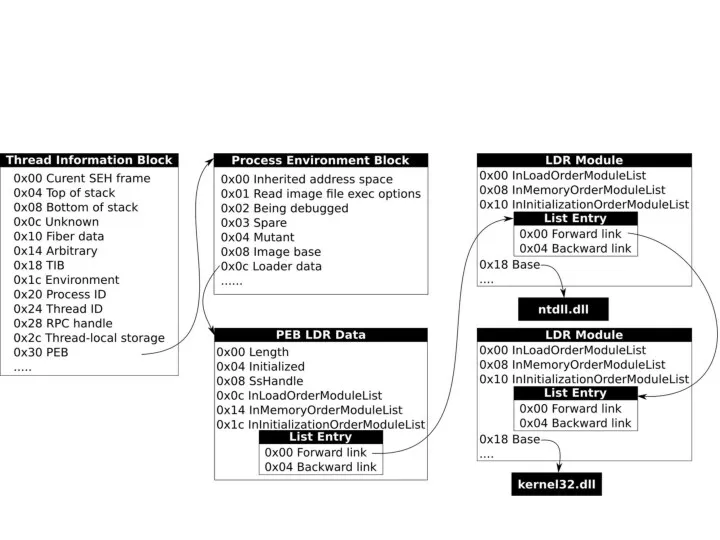

- 67. Thread Environment Block (TEB) Wow64 процессы в Windows имеют два PEB и два TEB. TEB создается

- 68. Thread Environment Block (TEB) [TEB+0] Указатель на первый SEH на стэке. [TEB+4] Указатель на конец области

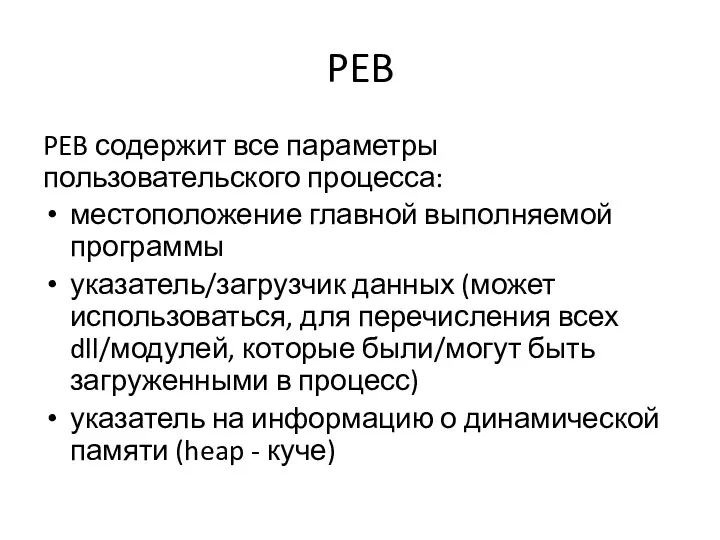

- 69. PEB PEB содержит все параметры пользовательского процесса: местоположение главной выполняемой программы указатель/загрузчик данных (может использоваться, для

- 70. PEB Находится в TIB[0x30], fs:[0x30] Для x64:

- 72. Системные таблицы SSDT IDT LDT

- 73. Системные вызовы INT 2e SYSENTER/SYSEXIT, SYSCALL/SYSRET ntdll_KiFastSystemCall Номер в таблице SSDT CreateFile->NtCreateFile->ZwCreateFile

- 75. Скачать презентацию

![Способы адресации [1] Регистровая адресация mov ax, bx Непосредственная адресация](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/200578/slide-30.jpg)

![Способы адресации [2] Косвенная адресация с масштабированием mov eax, [esi*3]+2](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/200578/slide-31.jpg)

![Управляющие структуры:switch-case mov eax, I shl bx, 1 jmp cs:jump_table[bx]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/200578/slide-52.jpg)

![Thread Environment Block (TEB) [TEB+0] Указатель на первый SEH на](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/200578/slide-67.jpg)

![PEB Находится в TIB[0x30], fs:[0x30] Для x64:](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/200578/slide-69.jpg)

Представление об информационной системе

Представление об информационной системе Компьютер – исполнитель алгоритмов

Компьютер – исполнитель алгоритмов Проект Перевод в Lazarus

Проект Перевод в Lazarus iSpring Suite

iSpring Suite Системы оптического распознавания документов

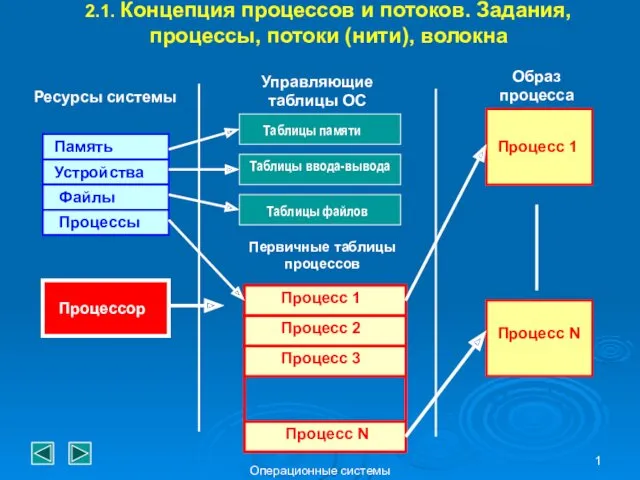

Системы оптического распознавания документов Концепция процессов и потоков. Задания, процессы, потоки, волокна

Концепция процессов и потоков. Задания, процессы, потоки, волокна Создание видеороликов. Мастер-класс

Создание видеороликов. Мастер-класс Информационные технологии

Информационные технологии Lirika V2

Lirika V2 Партицирование данных. Модели данных и нормализация таблиц. Урок 4

Партицирование данных. Модели данных и нормализация таблиц. Урок 4 Прерывания в системах DOS и BIOS. (Лекция 13)

Прерывания в системах DOS и BIOS. (Лекция 13) Хранение и передача информации

Хранение и передача информации Анимированные ребусы (презентация)

Анимированные ребусы (презентация) Элементы алгебры логики. Математические основы информатики

Элементы алгебры логики. Математические основы информатики Знакомство с языком программирования Python. Ввод. Вывод. Оператор присваивания. Математические операции

Знакомство с языком программирования Python. Ввод. Вывод. Оператор присваивания. Математические операции Группы безопасности. Управление пользователями

Группы безопасности. Управление пользователями презентация воскресенский

презентация воскресенский Робочий стіл та його об'єкти

Робочий стіл та його об'єкти Интерактивный тест для 8 класса по теме Информационная картина мира (ОВЗ)

Интерактивный тест для 8 класса по теме Информационная картина мира (ОВЗ) Основные этапы моделирования

Основные этапы моделирования Архитектура ОС MS Windows 2000+. Реестр

Архитектура ОС MS Windows 2000+. Реестр От „приставки“ до консоли. История игровых систем 1967 – наше время

От „приставки“ до консоли. История игровых систем 1967 – наше время Моделирование, как метод познания

Моделирование, как метод познания Игровые персонажи Dota 2

Игровые персонажи Dota 2 Действия с информацией

Действия с информацией Introduction to database management systems

Introduction to database management systems Правила создания презентаций

Правила создания презентаций Мир моиx увлечений: “Dota 2”

Мир моиx увлечений: “Dota 2”