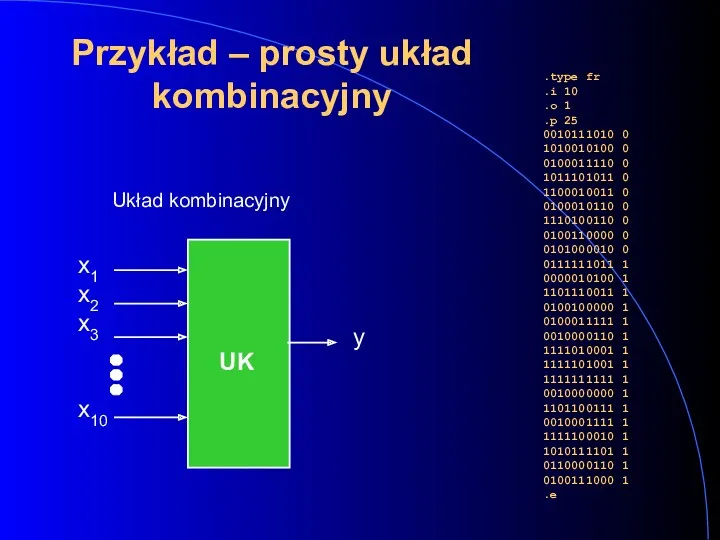

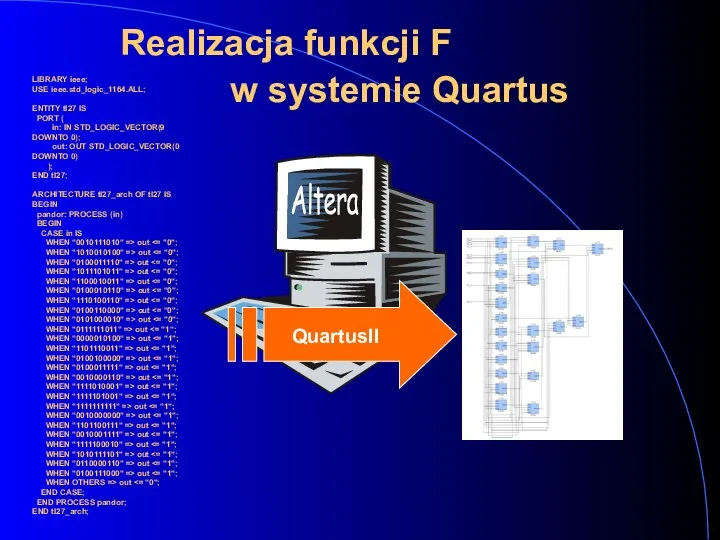

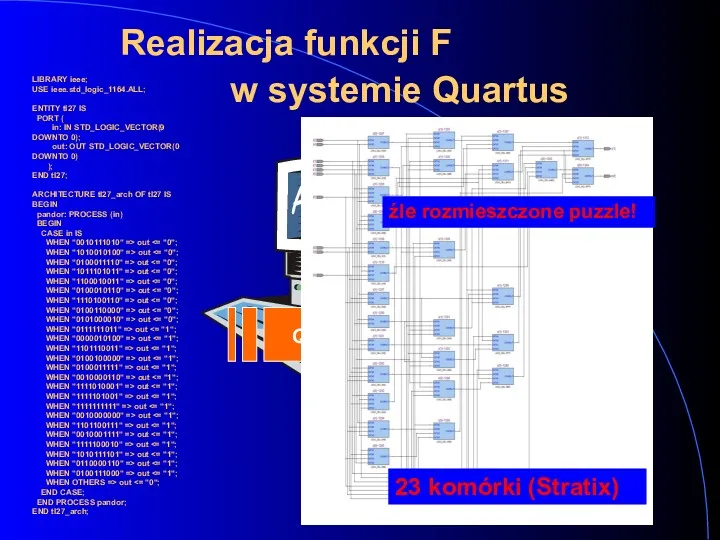

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY tl27 IS

PORT (

in: IN STD_LOGIC_VECTOR(9 DOWNTO

0);

out: OUT STD_LOGIC_VECTOR(0 DOWNTO 0)

);

END tl27;

ARCHITECTURE tl27_arch OF tl27 IS

BEGIN

pandor: PROCESS (in)

BEGIN

CASE in IS

WHEN "0010111010" => out <= "0";

WHEN "1010010100" => out <= "0";

WHEN "0100011110" => out <= "0";

WHEN "1011101011" => out <= "0";

WHEN "1100010011" => out <= "0";

WHEN "0100010110" => out <= "0";

WHEN "1110100110" => out <= "0";

WHEN "0100110000" => out <= "0";

WHEN "0101000010" => out <= "0";

WHEN "0111111011" => out <= "1";

WHEN "0000010100" => out <= "1";

WHEN "1101110011" => out <= "1";

WHEN "0100100000" => out <= "1";

WHEN "0100011111" => out <= "1";

WHEN "0010000110" => out <= "1";

WHEN "1111010001" => out <= "1";

WHEN "1111101001" => out <= "1";

WHEN "1111111111" => out <= "1";

WHEN "0010000000" => out <= "1";

WHEN "1101100111" => out <= "1";

WHEN "0010001111" => out <= "1";

WHEN "1111100010" => out <= "1";

WHEN "1010111101" => out <= "1";

WHEN "0110000110" => out <= "1";

WHEN "0100111000" => out <= "1";

WHEN OTHERS => out <= "0";

END CASE;

END PROCESS pandor;

END tl27_arch;

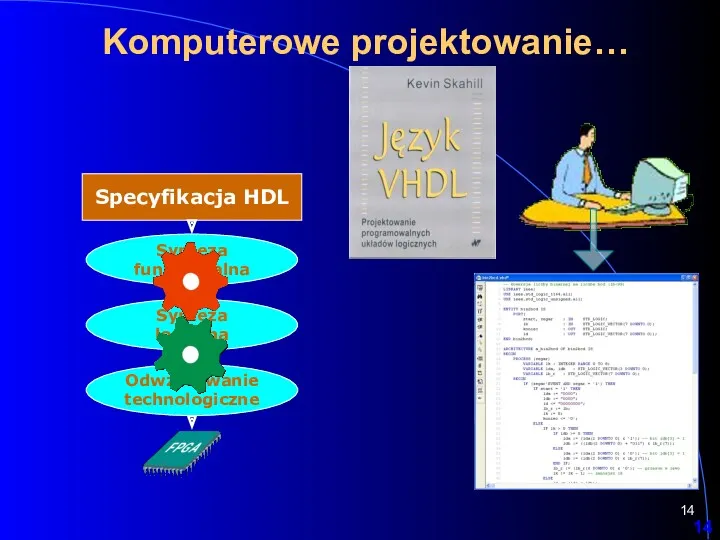

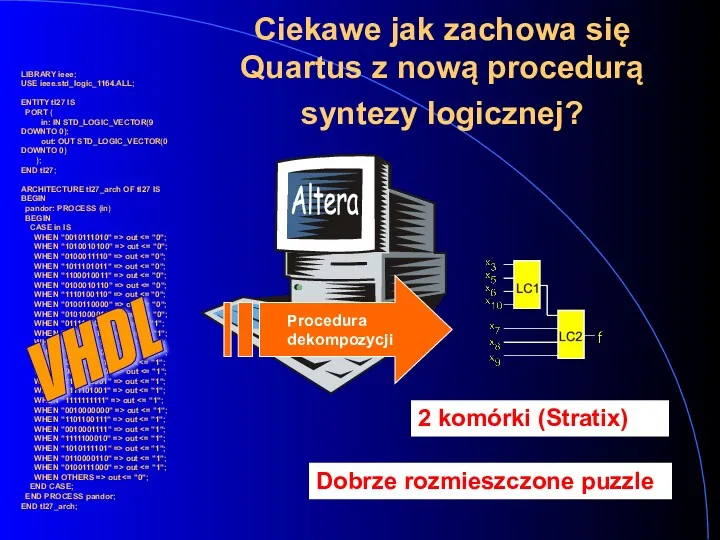

Ciekawe jak zachowa się Quartus z nową procedurą syntezy logicznej?

VHDL

2 komórki (Stratix)

Dobrze rozmieszczone puzzle

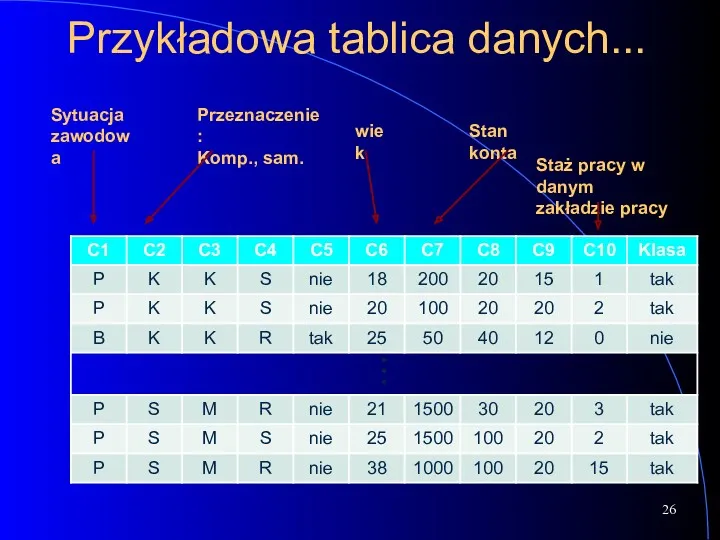

![Zastosowania [wiek > 25] & [stan konta > 70] &](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/239565/slide-26.jpg)

Подготовка к ГИА (часть А1). Умение оценивать количественные параметры информационных объектов. Задача 1

Подготовка к ГИА (часть А1). Умение оценивать количественные параметры информационных объектов. Задача 1 SAP CRM Система Управление взаимоотношениями с клиентами

SAP CRM Система Управление взаимоотношениями с клиентами Рисование в Adobe Photoshop

Рисование в Adobe Photoshop Интернет туралы түсінік

Интернет туралы түсінік Web-дизайн color:red;”> Урок 27. Css. Цвет и фон.Урок 28. Css. Свойства стиля списков.Форматирование HTML-документаТекст можно разделить тегами на смысловые блоки: заголовки, абзацы. Дополнительное разделение текста осуществляется переходом на но

Web-дизайн color:red;”> Урок 27. Css. Цвет и фон.Урок 28. Css. Свойства стиля списков.Форматирование HTML-документаТекст можно разделить тегами на смысловые блоки: заголовки, абзацы. Дополнительное разделение текста осуществляется переходом на но Practice -1. Installing Windows Server 2022. Windows System Administration

Practice -1. Installing Windows Server 2022. Windows System Administration МегаФон - Модем

МегаФон - Модем Преобразование диска с таблицей MBR – разделов в GPT- диск с помощью командной строки

Преобразование диска с таблицей MBR – разделов в GPT- диск с помощью командной строки Linux. Особенности и достоинства

Linux. Особенности и достоинства Формати аудіо- та відеофайлів

Формати аудіо- та відеофайлів Комп'ютерна графіка на ПЕОМ

Комп'ютерна графіка на ПЕОМ Системы искусственного интелекта

Системы искусственного интелекта Data mining - основные понятия и задачи

Data mining - основные понятия и задачи Управление реляционными базами данных. Языки определения данных и языки манипулирования данными

Управление реляционными базами данных. Языки определения данных и языки манипулирования данными Информационные технологии в организации учебного процесса. Информатизация общества

Информационные технологии в организации учебного процесса. Информатизация общества Системное программирование. Работа с консолью в Windows API

Системное программирование. Работа с консолью в Windows API Устройства резервного хранения информации

Устройства резервного хранения информации Системы счисления

Системы счисления Детективные квесты. Сюжетно-ролевые интеллектуальные игры

Детективные квесты. Сюжетно-ролевые интеллектуальные игры Таргетированная реклама

Таргетированная реклама Основы программирования: ТЕМА 05. ОРГАНИЗАЦИЯ ЦИКЛОВ.

Основы программирования: ТЕМА 05. ОРГАНИЗАЦИЯ ЦИКЛОВ. 30_WPF_технология_проектирования_приложений (2)

30_WPF_технология_проектирования_приложений (2) Программирование линейных алгоритмов

Программирование линейных алгоритмов Назначение САПР AutoCad. Основные примитивы AutoCad при создании графических объектов

Назначение САПР AutoCad. Основные примитивы AutoCad при создании графических объектов Техника безопасности при обслуживании информационных систем

Техника безопасности при обслуживании информационных систем Сайт ДА себе новому!

Сайт ДА себе новому! Компьютерные игры Need for Speed

Компьютерные игры Need for Speed презентация к уроку по информатике и ИКТ в 8 классе на тему: Основные компоненты компьютера и их функции

презентация к уроку по информатике и ИКТ в 8 классе на тему: Основные компоненты компьютера и их функции