Процессор. Элементы процессора. Устройство управления. Процессор Intel 8086. Команды. Кодирование команд. Подпрограммы презентация

Содержание

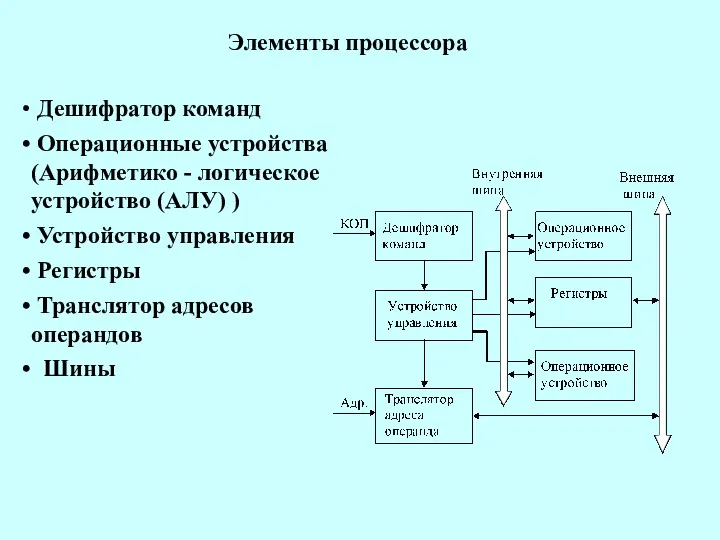

- 2. Элементы процессора Дешифратор команд Операционные устройства (Арифметико - логическое устройство (АЛУ) ) Устройство управления Регистры Транслятор

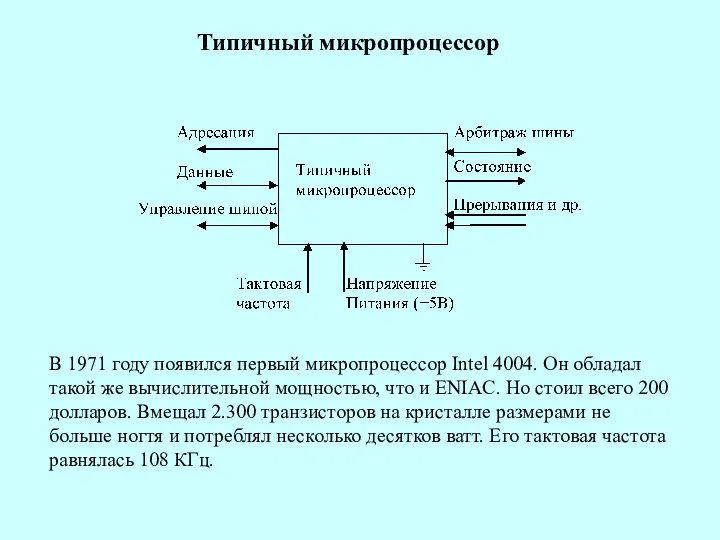

- 3. Типичный микропроцессор В 1971 году появился первый микропроцессор Intel 4004. Он обладал такой же вычислительной мощностью,

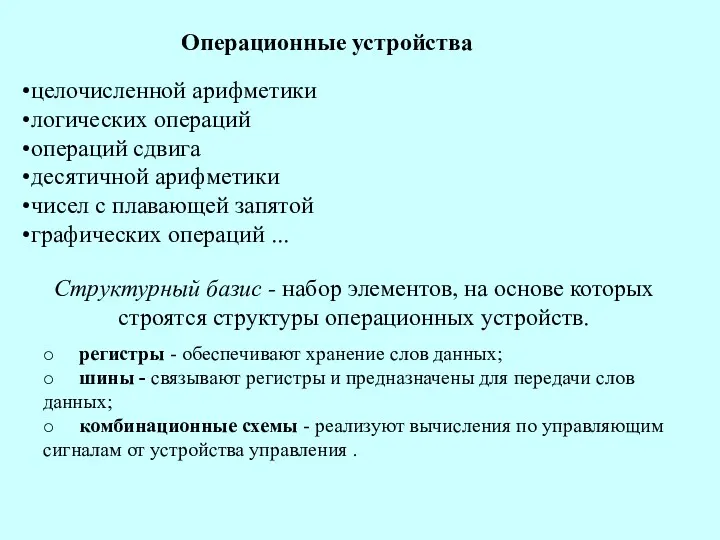

- 4. Операционные устройства целочисленной арифметики логических операций операций сдвига десятичной арифметики чисел с плавающей запятой графических операций

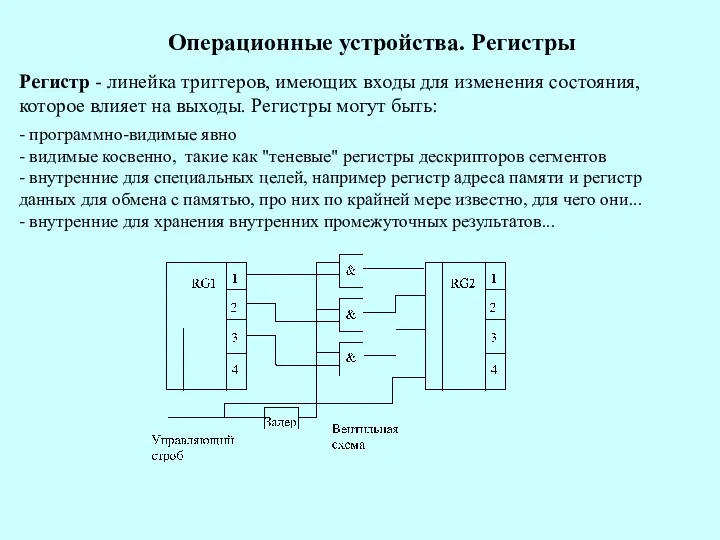

- 5. Операционные устройства. Регистры Регистр - линейка триггеров, имеющих входы для изменения состояния, которое влияет на выходы.

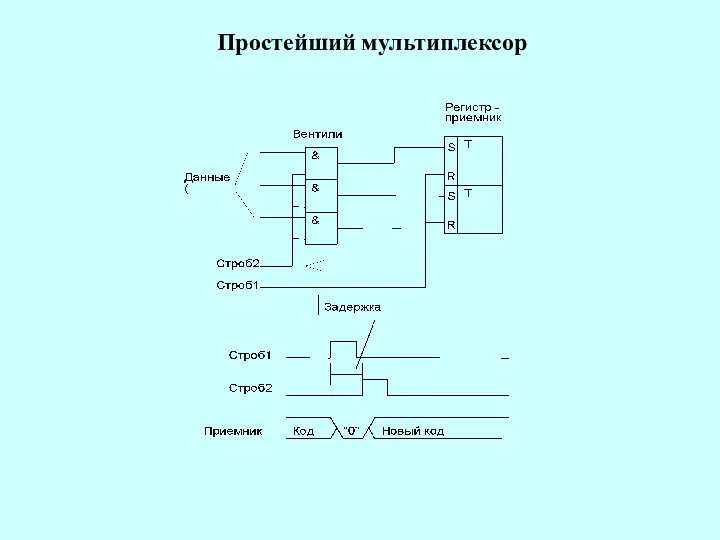

- 6. Простейший мультиплексор

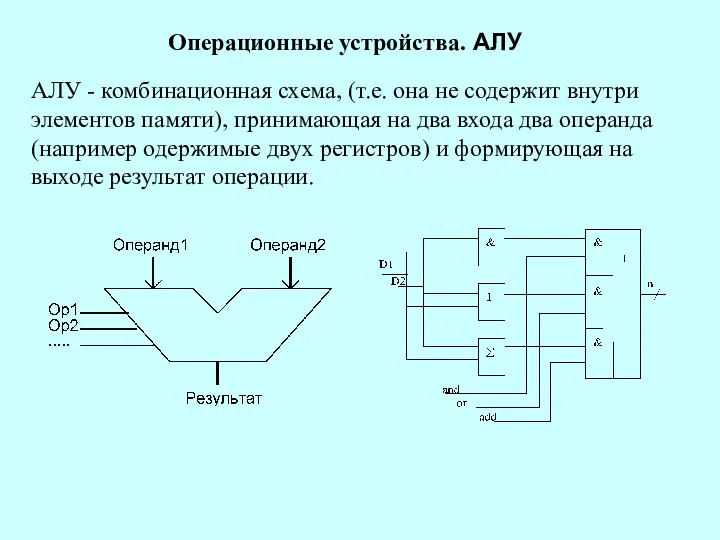

- 7. Операционные устройства. АЛУ АЛУ - комбинационная схема, (т.е. она не содержит внутри элементов памяти), принимающая на

- 8. АЛУ. Принципиальная схема. Состав Логическое устройство Полный сумматор Декодер операции

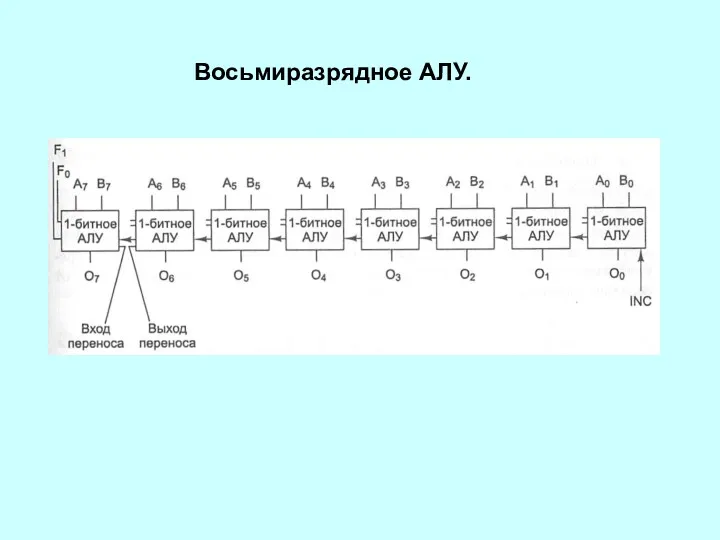

- 9. Восьмиразрядное АЛУ.

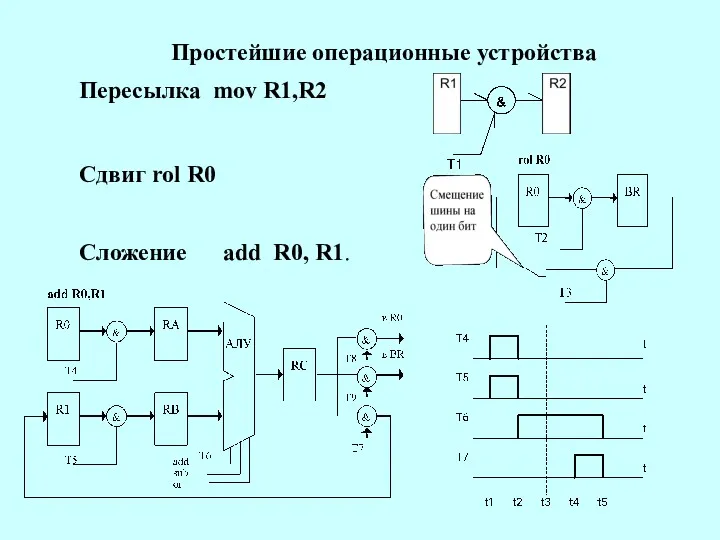

- 10. Простейшие операционные устройства Пересылка mov R1,R2 Сдвиг rol R0 Сложение add R0, R1.

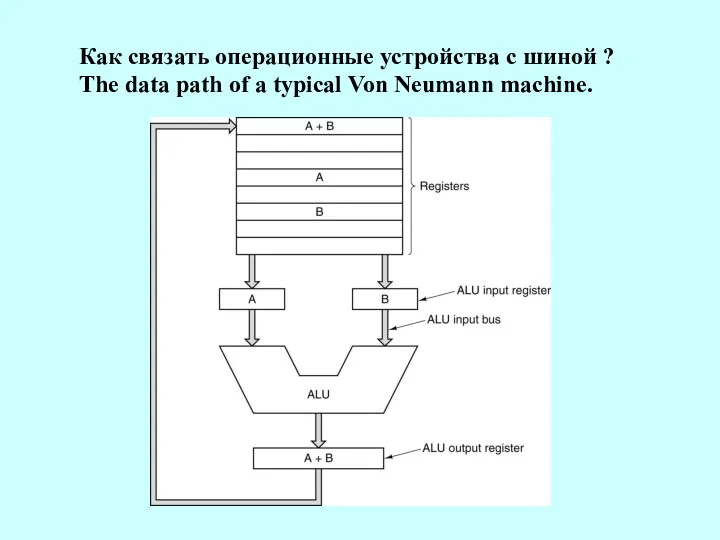

- 11. Как связать операционные устройства с шиной ? The data path of a typical Von Neumann machine.

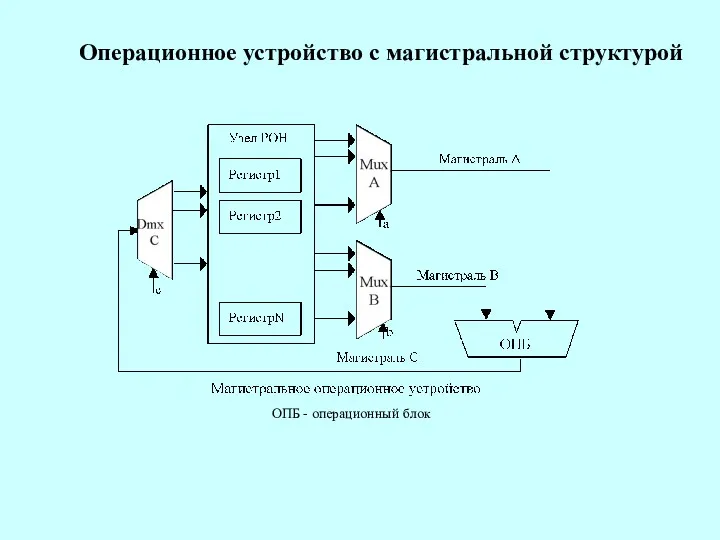

- 12. Операционное устройство с магистральной структурой ОПБ - операционный блок

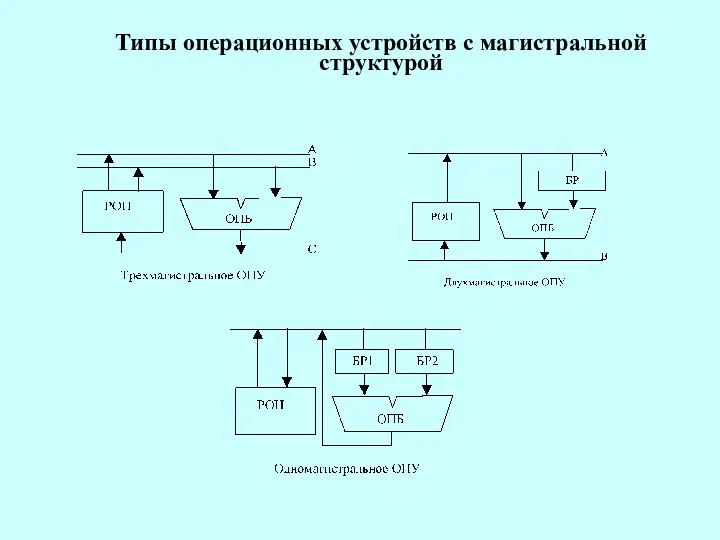

- 13. Типы операционных устройств с магистральной структурой

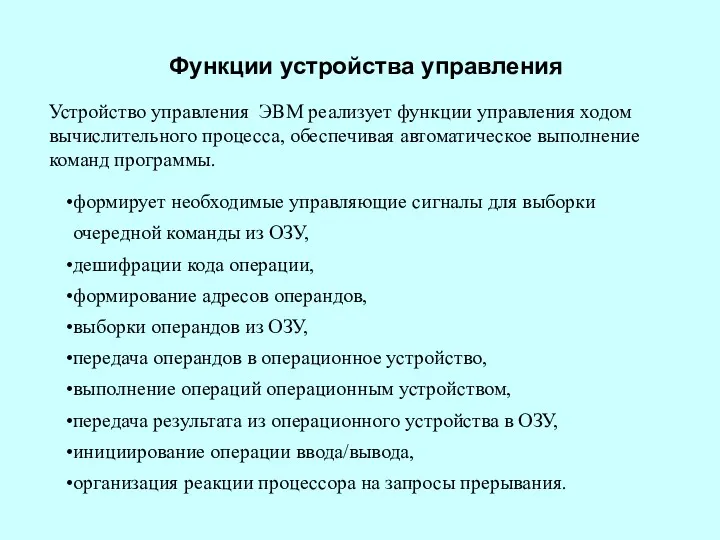

- 14. Устройство управления ЭВМ реализует функции управления ходом вычислительного процесса, обеспечивая автоматическое выполнение команд программы. Функции устройства

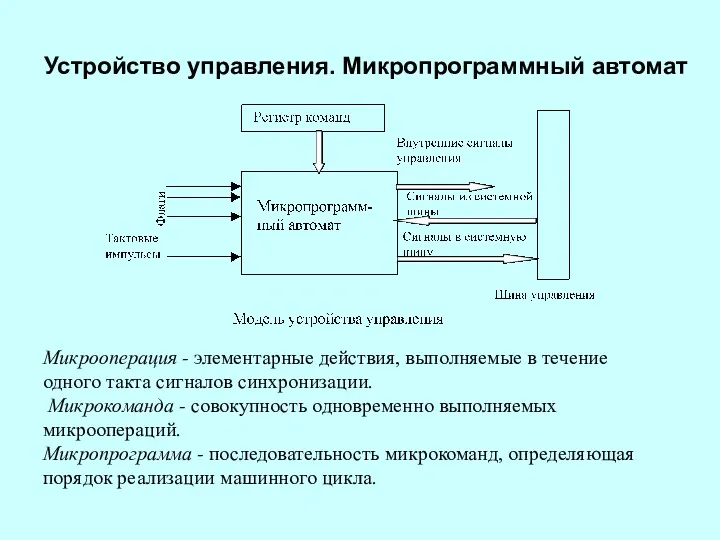

- 15. Устройство управления. Микропрограммный автомат Микрооперация - элементарные действия, выполняемые в течение одного такта сигналов синхронизации. Микрокоманда

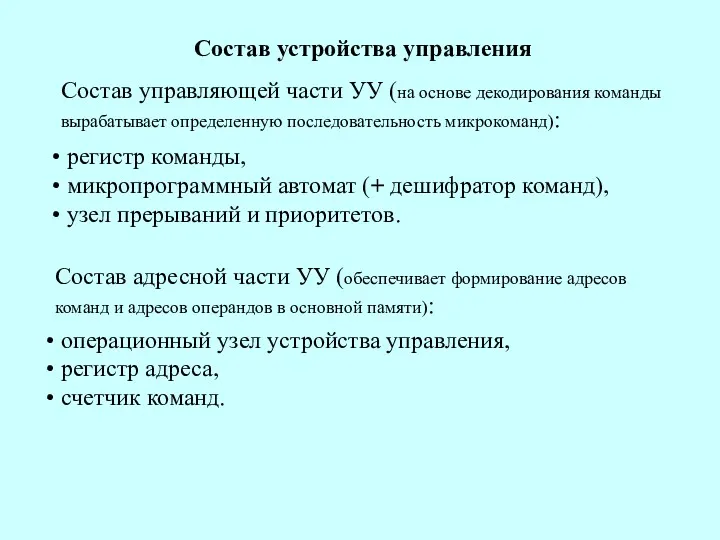

- 16. Состав управляющей части УУ (на основе декодирования команды вырабатывает определенную последовательность микрокоманд): регистр команды, микропрограммный автомат

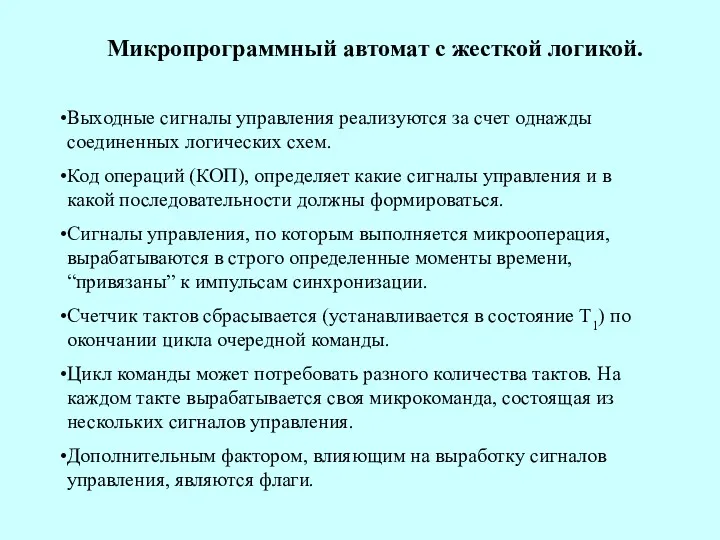

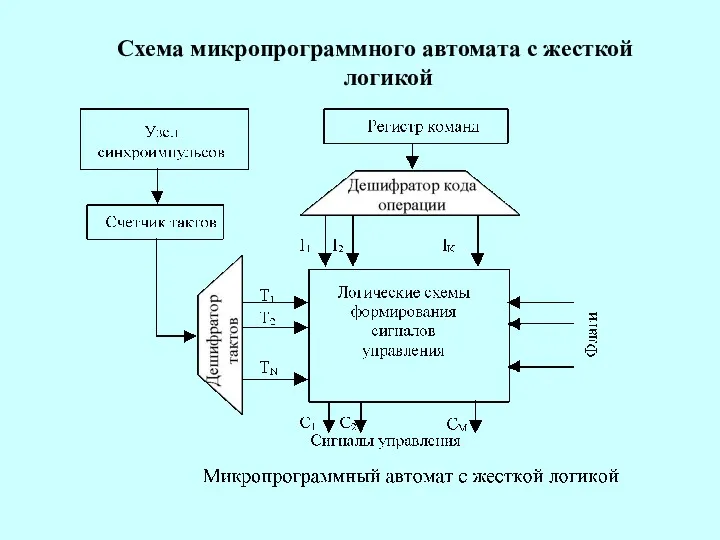

- 17. Микропрограммный автомат с жесткой логикой. Выходные сигналы управления реализуются за счет однажды соединенных логических схем. Код

- 18. Схема микропрограммного автомата с жесткой логикой

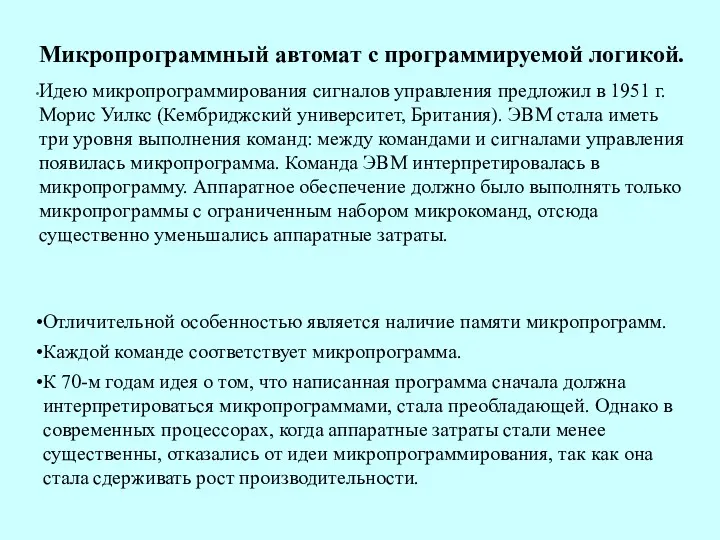

- 19. Микропрограммный автомат с программируемой логикой. Идею микропрограммирования сигналов управления предложил в 1951 г. Морис Уилкс (Кембриджский

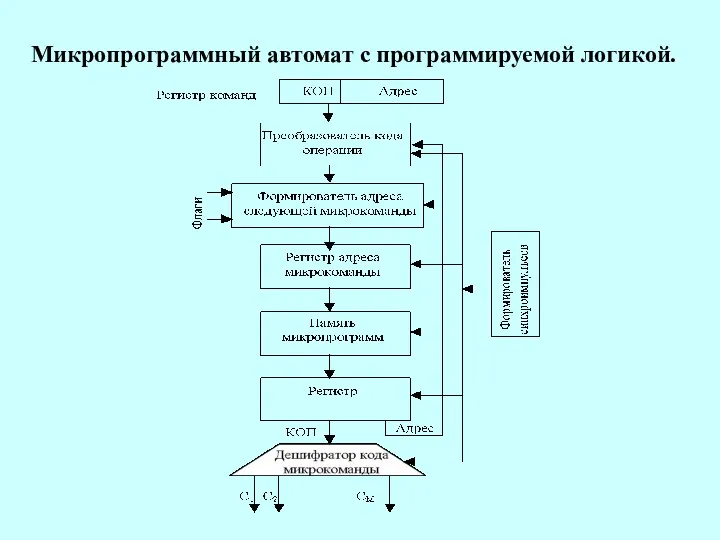

- 20. Микропрограммный автомат с программируемой логикой.

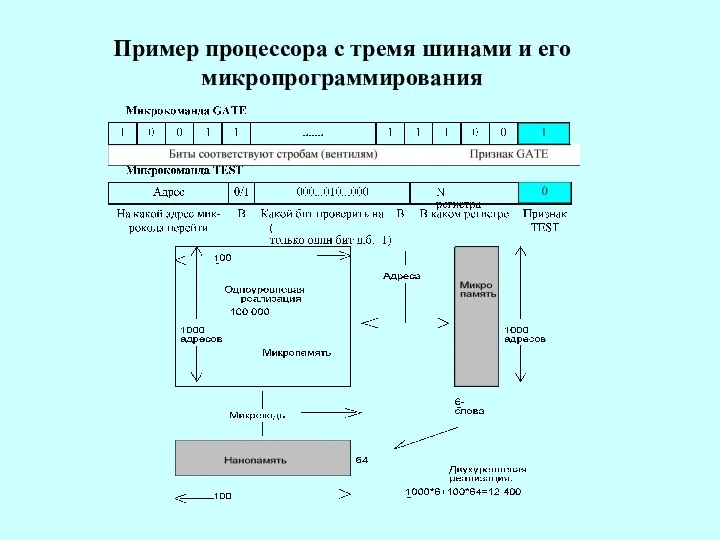

- 21. Пример процессора с тремя шинами и его микропрограммирования

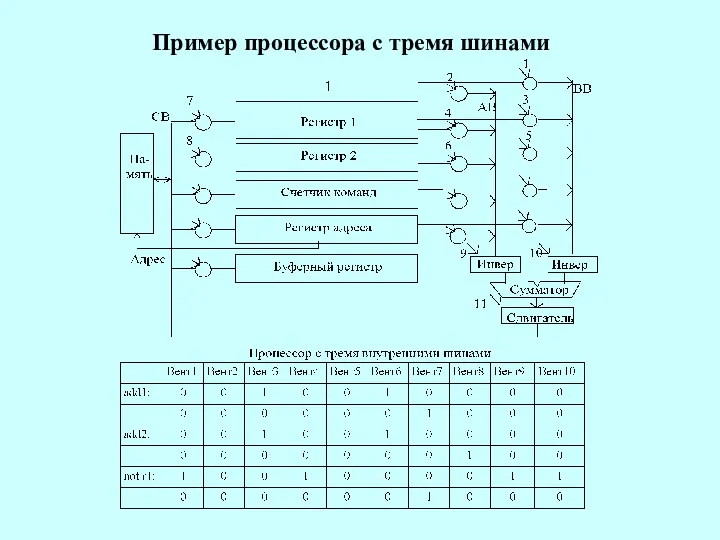

- 22. Пример процессора с тремя шинами

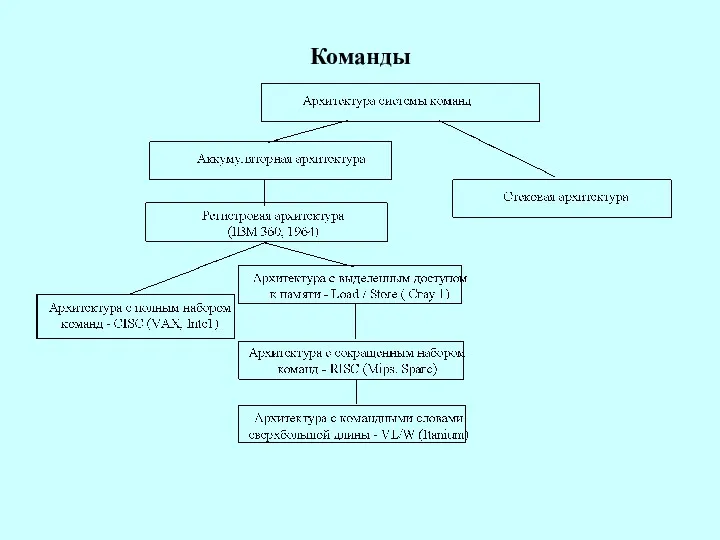

- 23. Команды Важную роль в выборе архитектуры системы команд играет ответ на вопрос о том, где могут

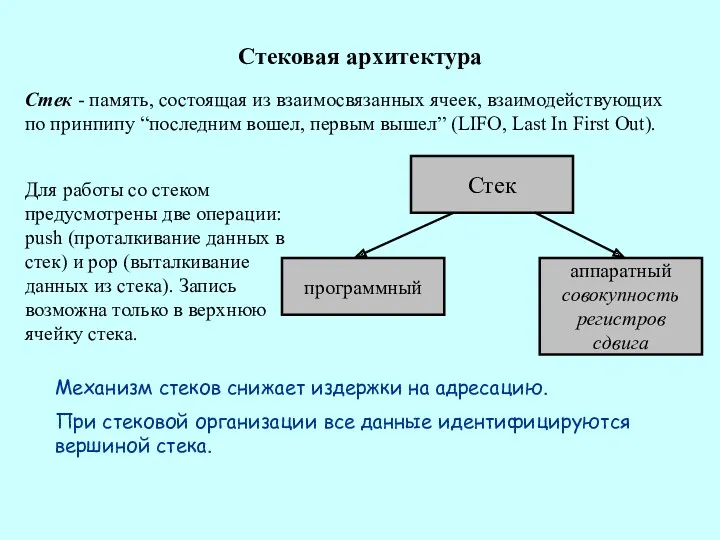

- 24. Стековая архитектура Стек - память, состоящая из взаимосвязанных ячеек, взаимодействующих по принпипу “последним вошел, первым вышел”

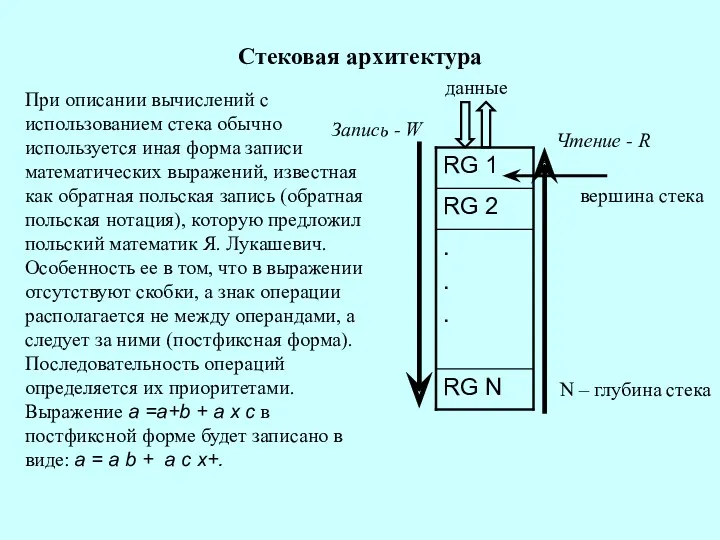

- 25. Стековая архитектура При описании вычислений с использованием стека обычно используется иная форма записи математических выражений, известная

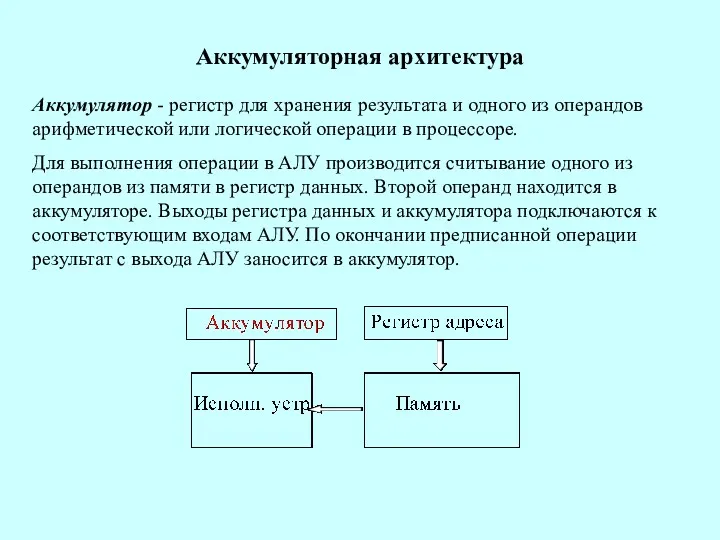

- 26. Аккумуляторная архитектура Аккумулятор - регистр для хранения результата и одного из операндов арифметической или логической операции

- 27. Аккумуляторная архитектура 2 Для загрузки в аккумулятор содержимого ячейки х предусмотрена команда загрузки load х. Запись

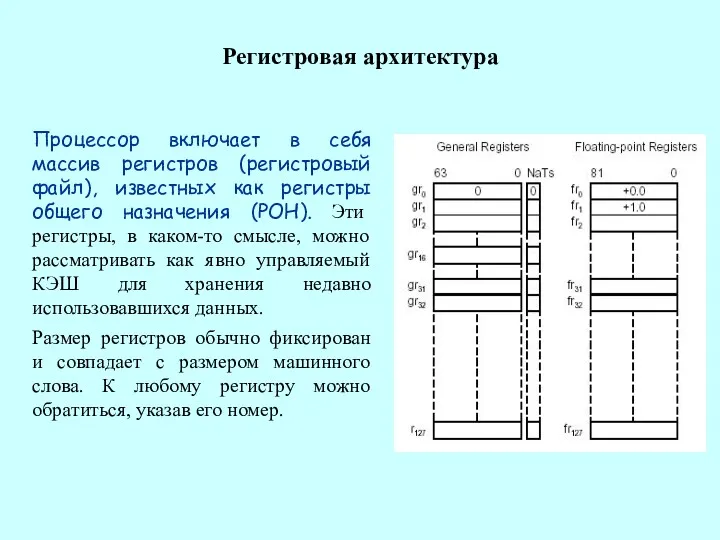

- 28. Регистровая архитектура Процессор включает в себя массив регистров (регистровый файл), известных как регистры общего назначения (РОН).

- 29. Регистровая архитектура Количество РОН в архитектурах типа CISC обычно невелико. RISС-архитектура предполагает использование существенно большего числа

- 30. Архитектура с выделенным доступом к памяти В архитектуре с выделенным доступом к памяти обращение к основной

- 31. Команды

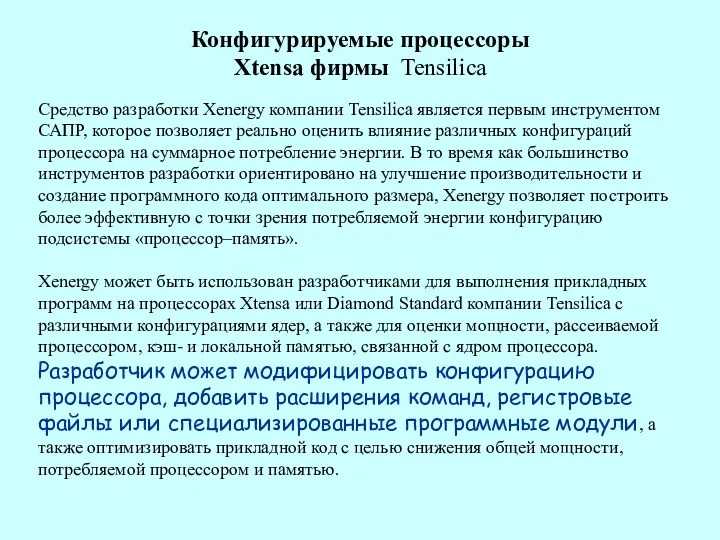

- 32. Конфигурируемые процессоры Xtensa фирмы Tensilica Средство разработки Xenergy компании Tensilica является первым инструментом САПР, которое позволяет

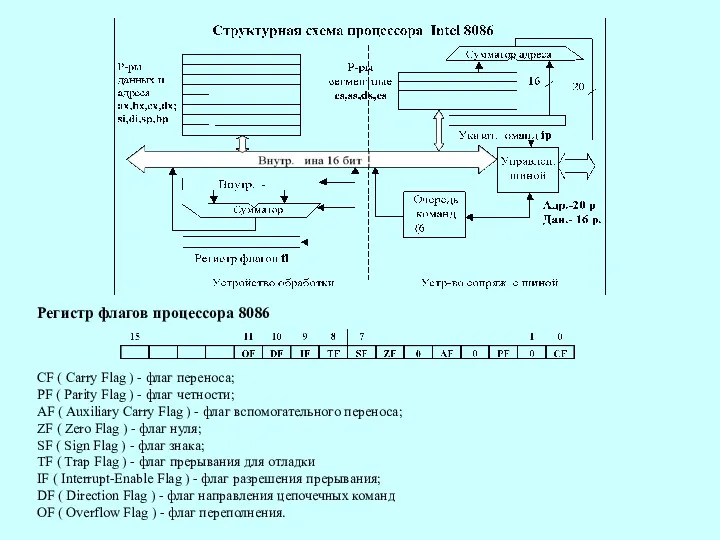

- 33. CF ( Carry Flag ) - флаг переноса; PF ( Parity Flag ) - флаг четности;

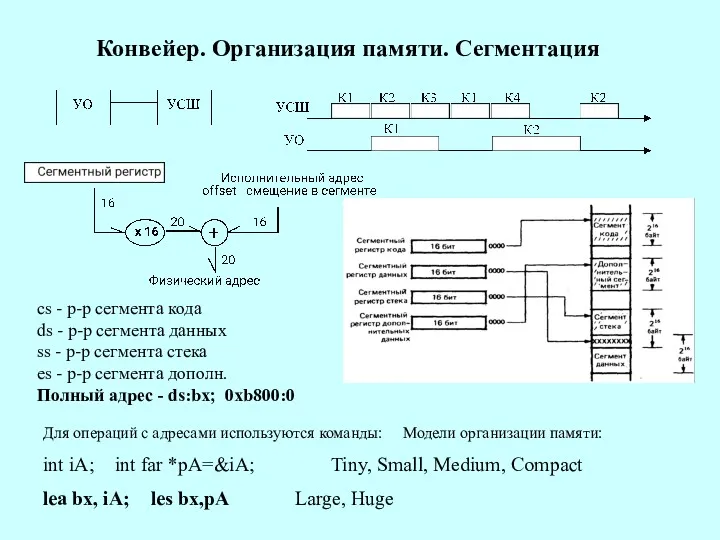

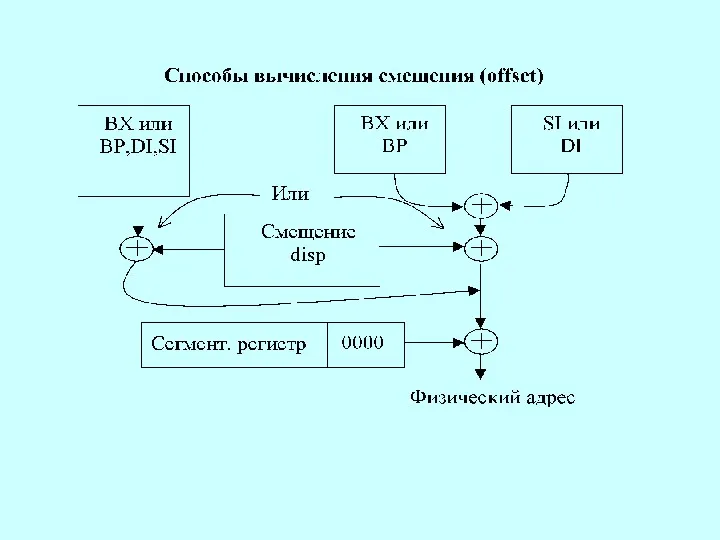

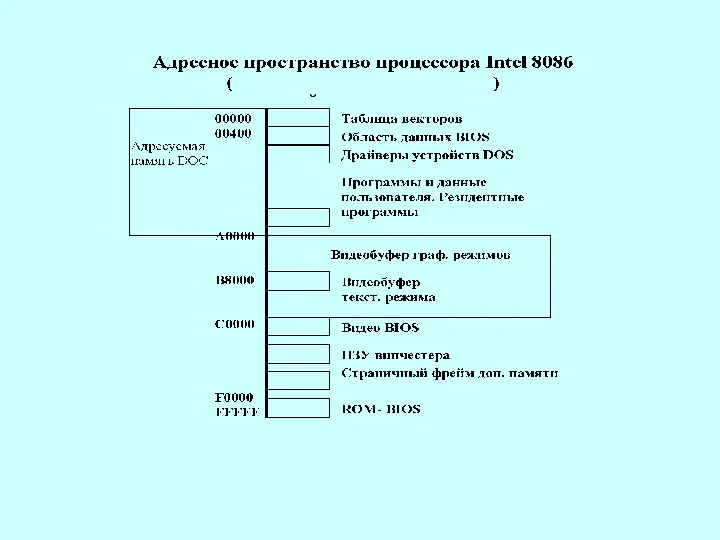

- 34. Конвейер. Организация памяти. Сегментация cs - р-р сегмента кода ds - р-р сегмента данных ss -

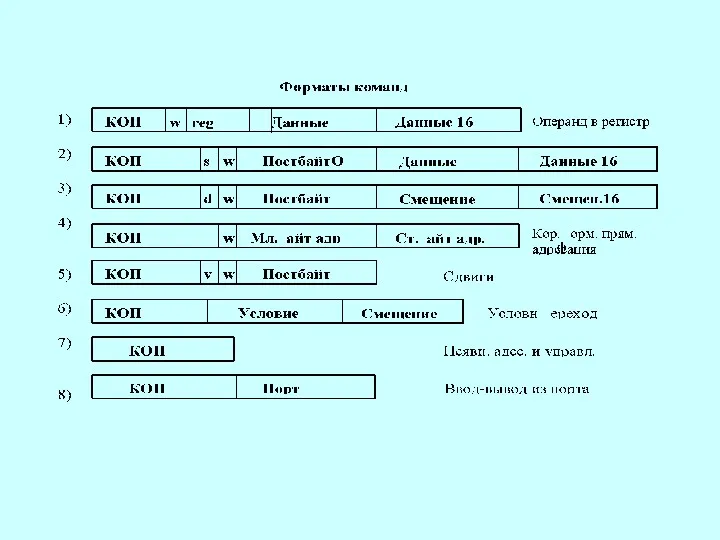

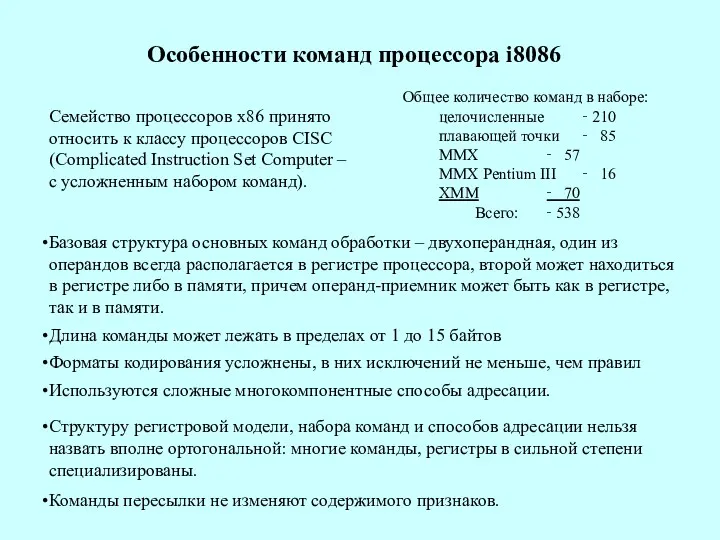

- 36. Особенности команд процессора i8086 Семейство процессоров х86 принято относить к классу процессоров CISC (Complicated Instruction Set

- 37. 1. Команды пересылки. 1.1.Пересылки общего назначения MOV eax, [ebx] 1.2. Пересылки из/в стек: PUSH (втолкнуть в

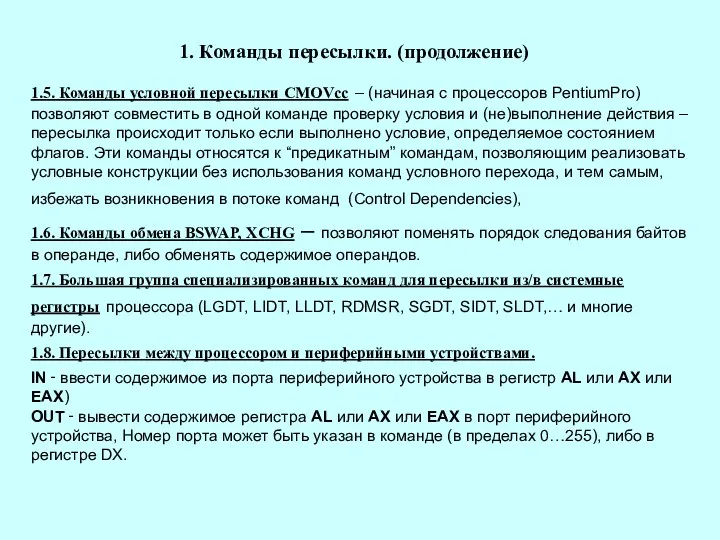

- 38. 1. Команды пересылки. (продолжение) 1.5. Команды условной пересылки CMOVcc – (начиная с процессоров PentiumPro) позволяют совместить

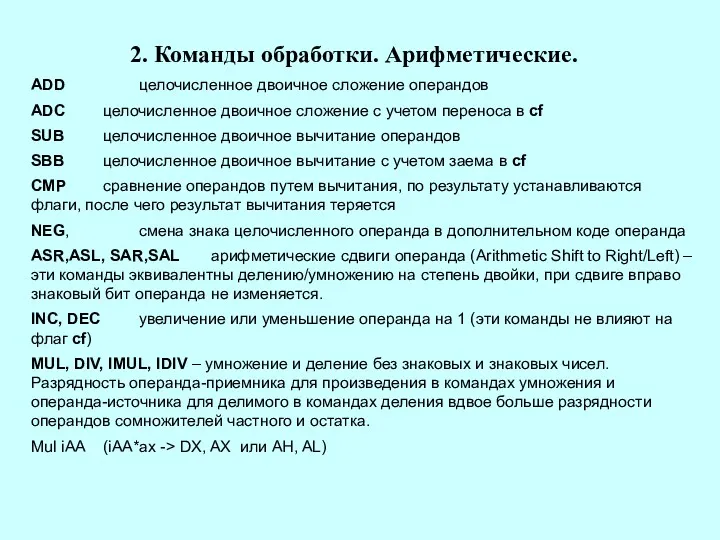

- 39. 2. Команды обработки. Арифметические. ADD целочисленное двоичное сложение операндов ADC целочисленное двоичное сложение с учетом переноса

- 40. 2. Команды обработки. Логические. OR - . Это команда побитовой установки (т.е. записи “единицы” в заданные

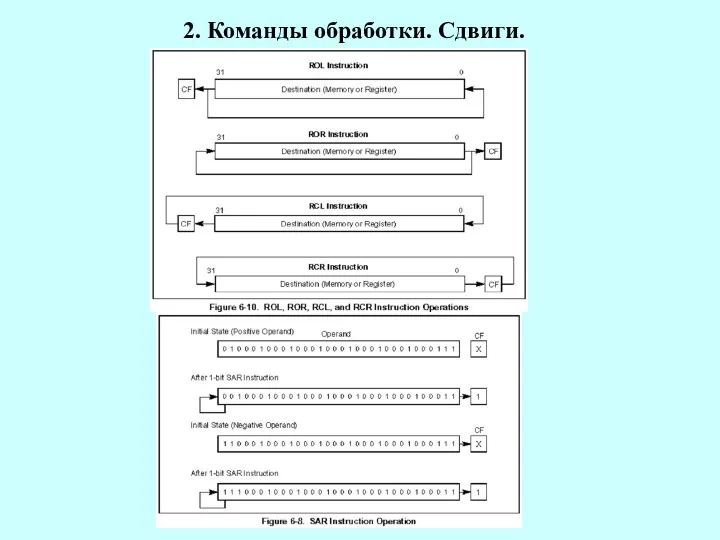

- 41. 2. Команды обработки. Сдвиги. В процессорах 386+ реализовано 5 видов операции сдвигов, которые различаются тем, что

- 42. 2. Команды обработки. Сдвиги.

- 43. 3. Проверки и передача управления. 3.1. Команды проверки и сравнения CMP - сравнение операндов путем вычитания.

- 44. Формат двухоперандной команды [Префикс] КОП [постбайт адресации] [смещение] [непоср.операнд]

- 45. Полный формат двухоперандной команды Add [eax+2*ebx],ecx 000000 01 00 001 100 01 011 000

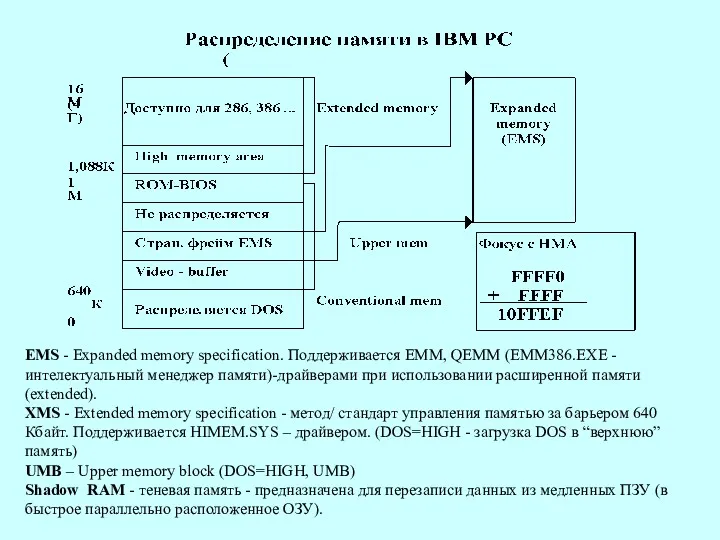

- 48. EMS - Expanded memory specification. Поддерживается ЕММ, QЕММ (ЕММ386.EXE - интелектуальный менеджер памяти)-драйверами при использовании расширенной

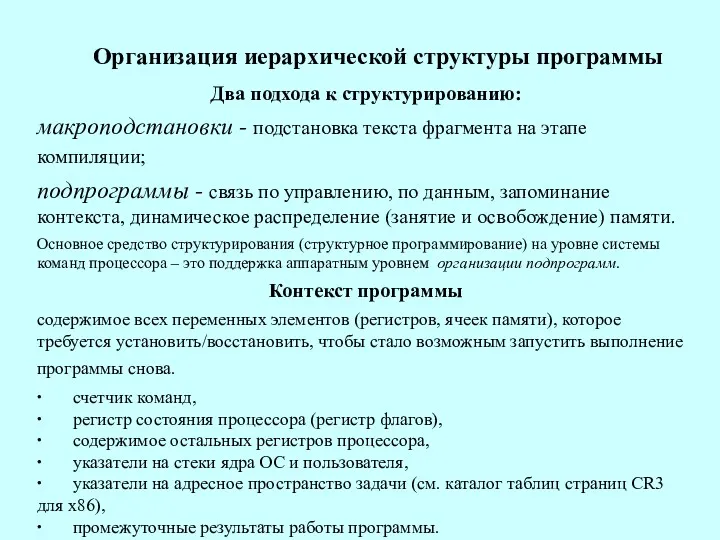

- 49. Организация иерархической структуры программы Два подхода к структурированию: макроподстановки - подстановка текста фрагмента на этапе компиляции;

- 50. Для облегчения сохранения-восстановления контекста в разных реализациях процессоров могут быть использованы: 1) Специальные команды: В iх86+

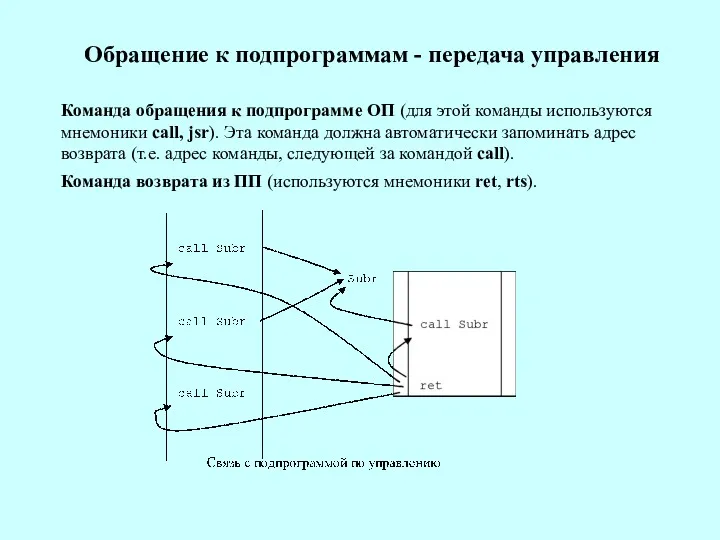

- 51. Обращение к подпрограммам - передача управления Команда обращения к подпрограмме ОП (для этой команды используются мнемоники

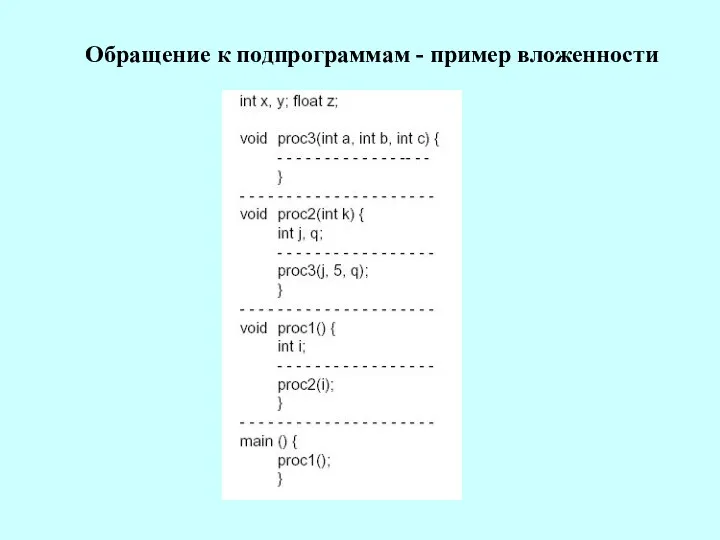

- 52. Обращение к подпрограммам - пример вложенности

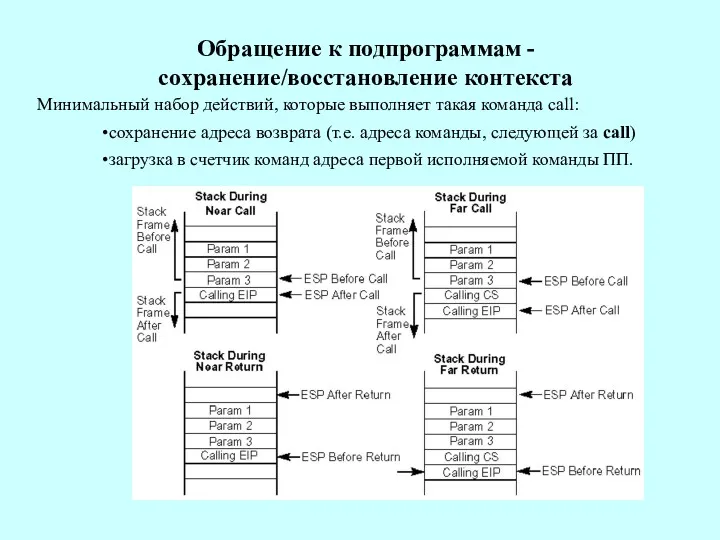

- 53. Обращение к подпрограммам - сохранение/восстановление контекста Минимальный набор действий, которые выполняет такая команда call: сохранение адреса

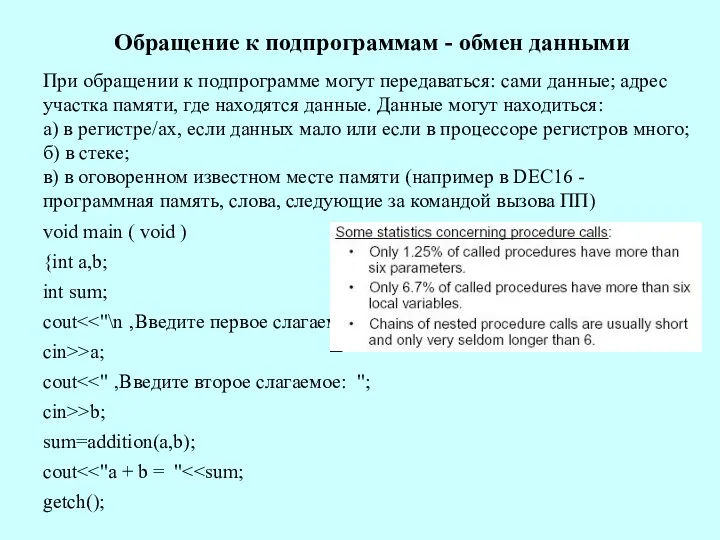

- 54. Обращение к подпрограммам - обмен данными При обращении к подпрограмме могут передаваться: сами данные; адрес участка

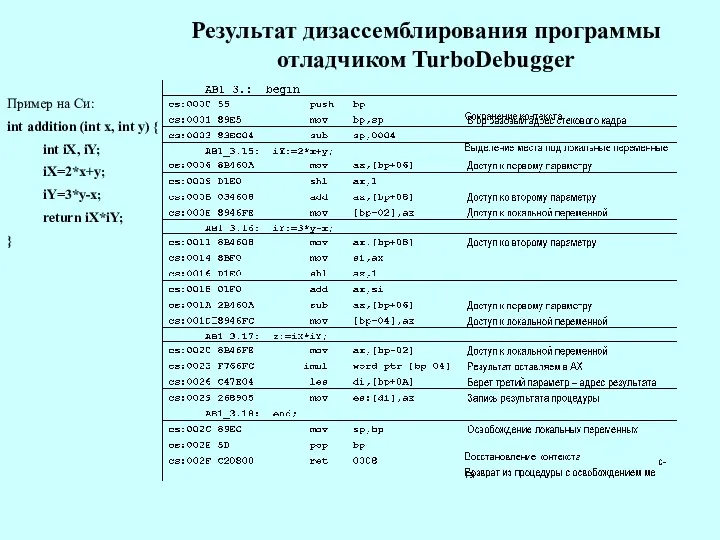

- 55. Результат дизассемблирования программы отладчиком TurboDebugger Пример на Си: int addition (int x, int y) { int

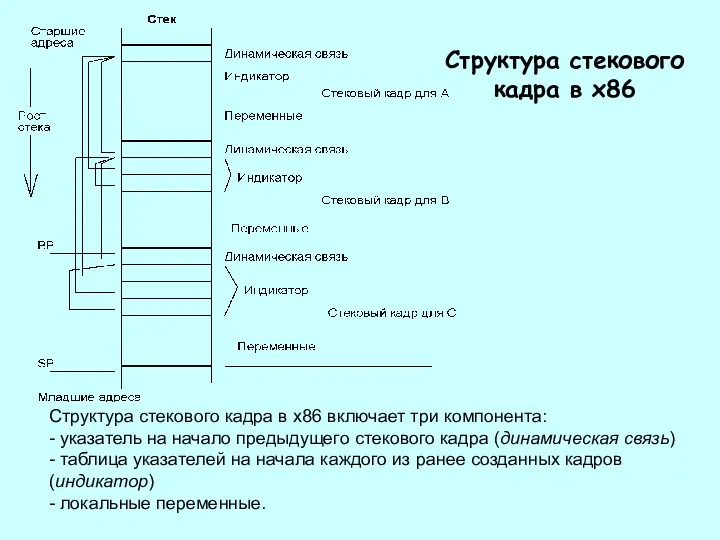

- 56. Структура стекового кадра в х86 Структура стекового кадра в х86 включает три компонента: - указатель на

- 58. Скачать презентацию

![1. Команды пересылки. 1.1.Пересылки общего назначения MOV eax, [ebx] 1.2.](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/283532/slide-36.jpg)

![Формат двухоперандной команды [Префикс] КОП [постбайт адресации] [смещение] [непоср.операнд]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/283532/slide-43.jpg)

![Полный формат двухоперандной команды Add [eax+2*ebx],ecx 000000 01 00 001 100 01 011 000](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/283532/slide-44.jpg)

Қолданбалы программалар пакеті

Қолданбалы программалар пакеті Дизайн web-проекта

Дизайн web-проекта Измерение информации

Измерение информации Онлайн-активность

Онлайн-активность Алгоритмы с повторением

Алгоритмы с повторением Технология хранения, поиска, сортировки данных

Технология хранения, поиска, сортировки данных Ветвление

Ветвление Стандартные вспомогательные средства. Пакет java.util. (Тема 12)

Стандартные вспомогательные средства. Пакет java.util. (Тема 12) Проектирование информационной системы для автоматизации технических осмотров автомобилей

Проектирование информационной системы для автоматизации технических осмотров автомобилей Компьютерные программы, используемые при автоматизации работы парикмахерских и салонов красоты

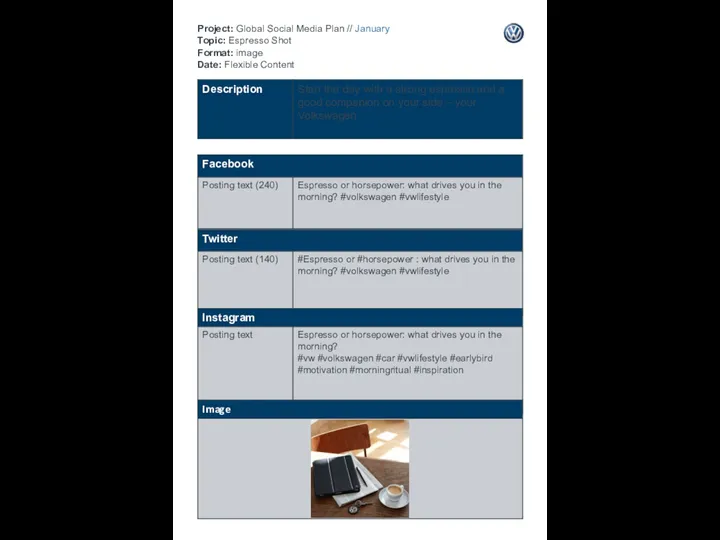

Компьютерные программы, используемые при автоматизации работы парикмахерских и салонов красоты Global Social Media Plan

Global Social Media Plan Принципы геолого-технологического моделирования (построение куба литофаций)

Принципы геолого-технологического моделирования (построение куба литофаций) Общие проблемы

Общие проблемы Архитектура платформы MS .NET

Архитектура платформы MS .NET MS Excel для построения линейной регрессионной модели

MS Excel для построения линейной регрессионной модели Проблемы и решения при создании графики

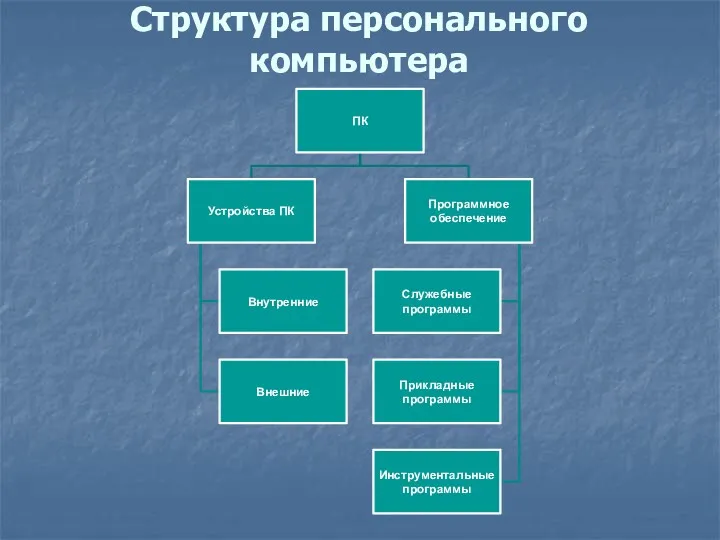

Проблемы и решения при создании графики Структура персонального компьютера

Структура персонального компьютера Защита урока информатики в 11 классе

Защита урока информатики в 11 классе Типология телеканалов

Типология телеканалов Презентация Кодирование графической информации. Мой компьютерный герой, 6 класс

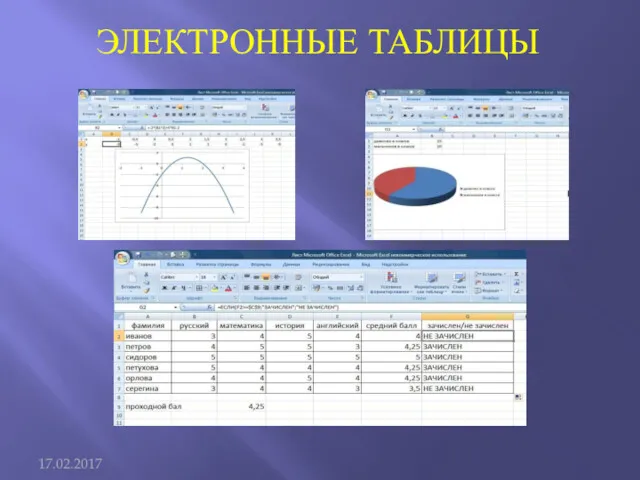

Презентация Кодирование графической информации. Мой компьютерный герой, 6 класс Электронные таблицы

Электронные таблицы Информатика. Инструкция к тестированию

Информатика. Инструкция к тестированию Інтегроване використання засобів опрацювання документів

Інтегроване використання засобів опрацювання документів Каноническое проектирование информационных систем

Каноническое проектирование информационных систем Правила поведения в Интернете

Правила поведения в Интернете Презентация Перевод чисел между системами счисления, основания которых являются степенями числа 2 10 класс

Презентация Перевод чисел между системами счисления, основания которых являются степенями числа 2 10 класс Урок-игра по информатике В гостях у Смешариков. Диск

Урок-игра по информатике В гостях у Смешариков. Диск Java 8 Stream API

Java 8 Stream API