Содержание

- 2. Развитие интерфейсов накопителей IDE SATA

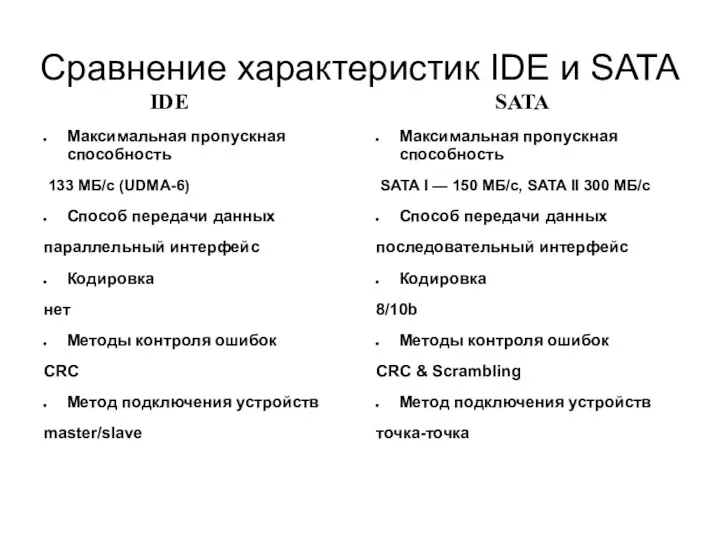

- 3. Сравнение характеристик IDE и SATA Максимальная пропускная способность 133 МБ/с (UDMA-6) Способ передачи данных параллельный интерфейс

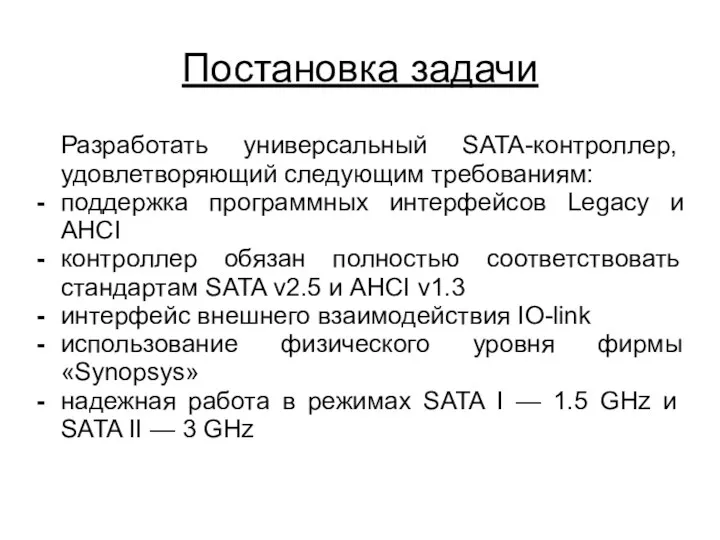

- 4. Постановка задачи Разработать универсальный SATA-контроллер, удовлетворяющий следующим требованиям: - поддержка программных интерфейсов Legacy и AHCI -

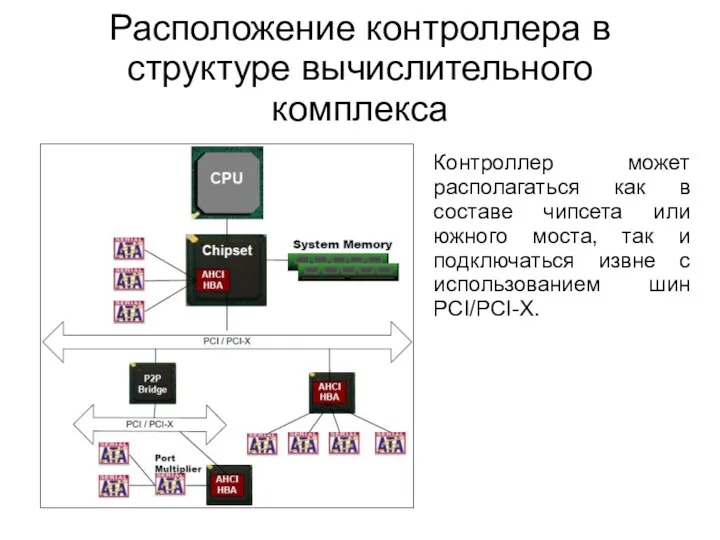

- 5. Расположение контроллера в структуре вычислительного комплекса Контроллер может располагаться как в составе чипсета или южного моста,

- 6. Схема функциональных уровней стандарта SATA - Commands and Application ― верхний уровень, обрабатывающий поступающие команды, работающий

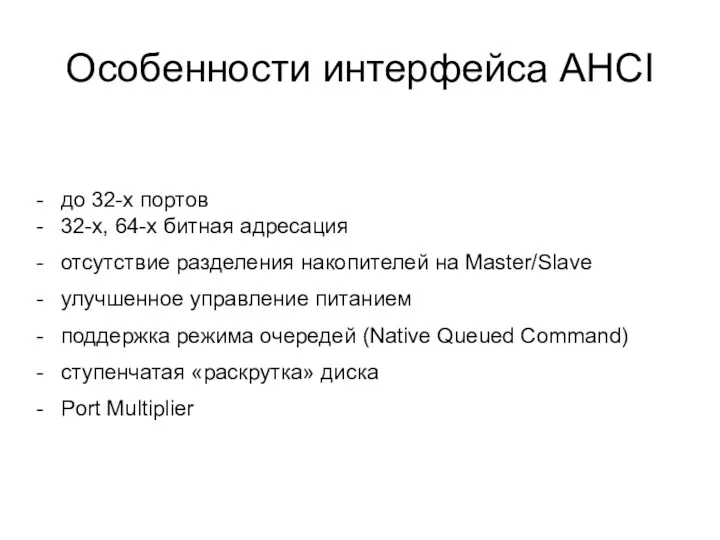

- 7. Особенности интерфейса AHCI - до 32-х портов - 32-х, 64-х битная адресация - отсутствие разделения накопителей

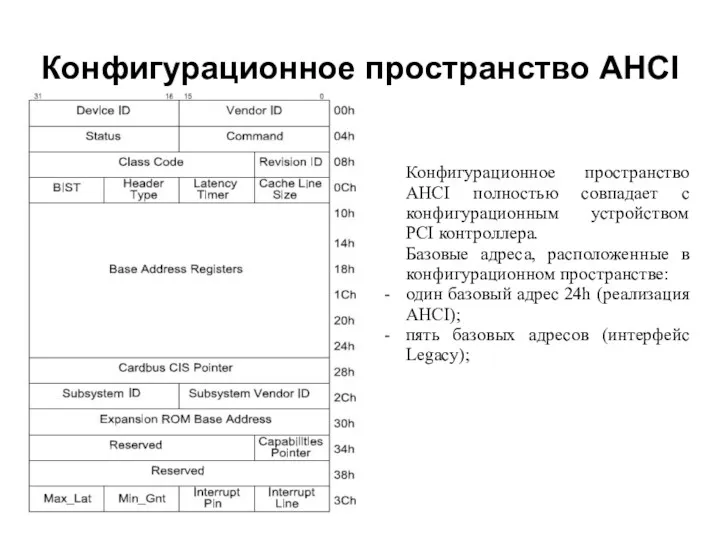

- 8. Конфигурационное пространство AHCI Конфигурационное пространство AHCI полностью совпадает с конфигурационным устройством PCI контроллера. Базовые адреса, расположенные

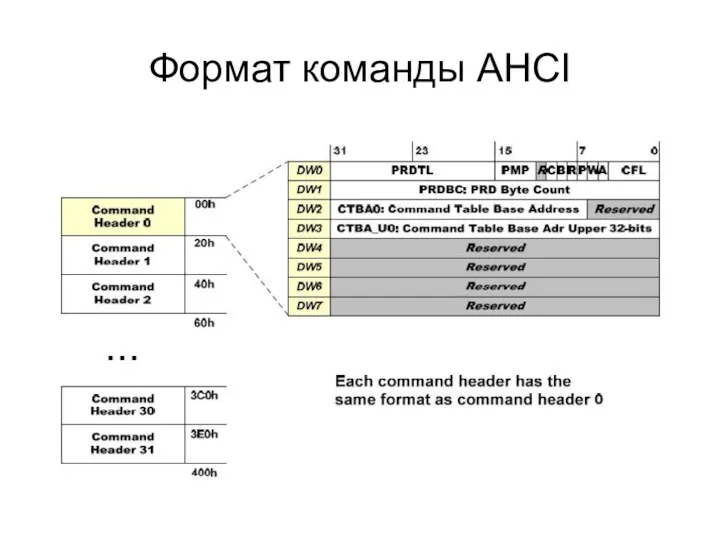

- 9. Формат команды AHCI

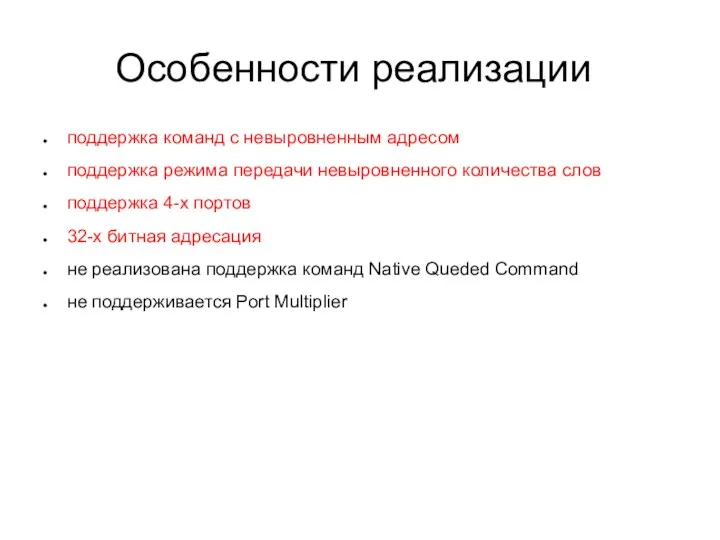

- 10. Особенности реализации поддержка команд с невыровненным адресом поддержка режима передачи невыровненного количества слов поддержка 4-х портов

- 11. Реализация - IO-link client ― модуль, отвечающий за проведение транзакций на IO-link-интерфейсе; - SATA ― IO-link

- 12. Внутреннее устройство модуля SATA-port

- 13. Автомат, реализующий DMA транзакции на AHCI уровне

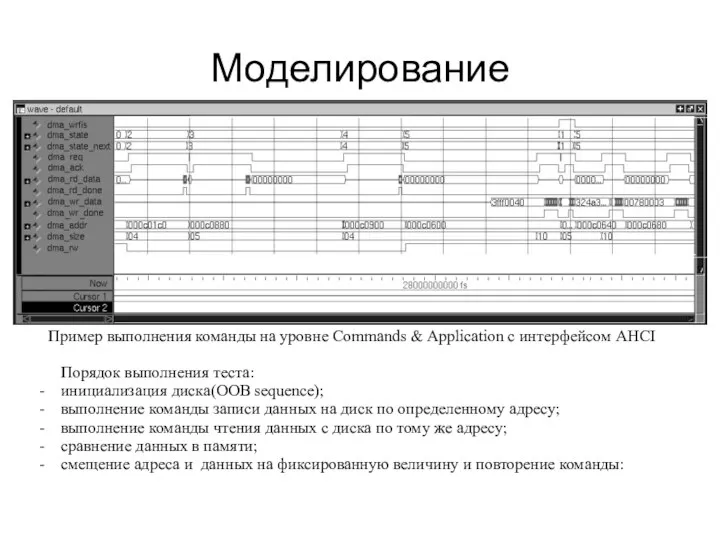

- 14. Моделирование Пример выполнения команды на уровне Commands & Application с интерфейсом AHCI Порядок выполнения теста: инициализация

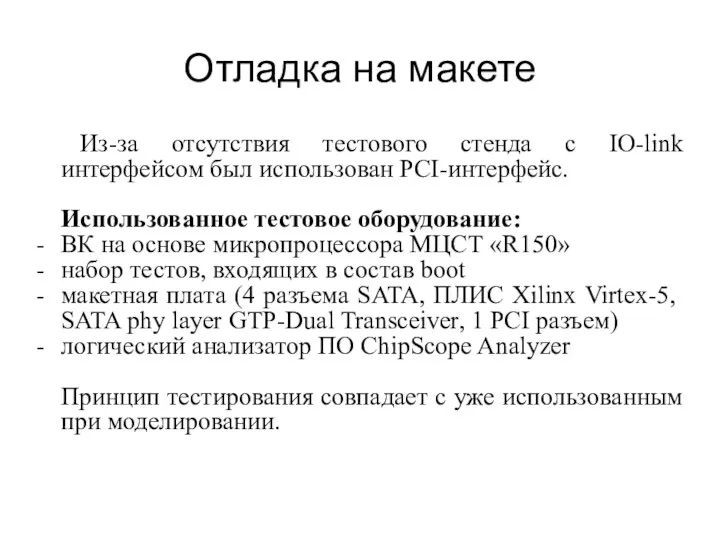

- 15. Отладка на макете Из-за отсутствия тестового стенда с IO-link интерфейсом был использован PCI-интерфейс. Использованное тестовое оборудование:

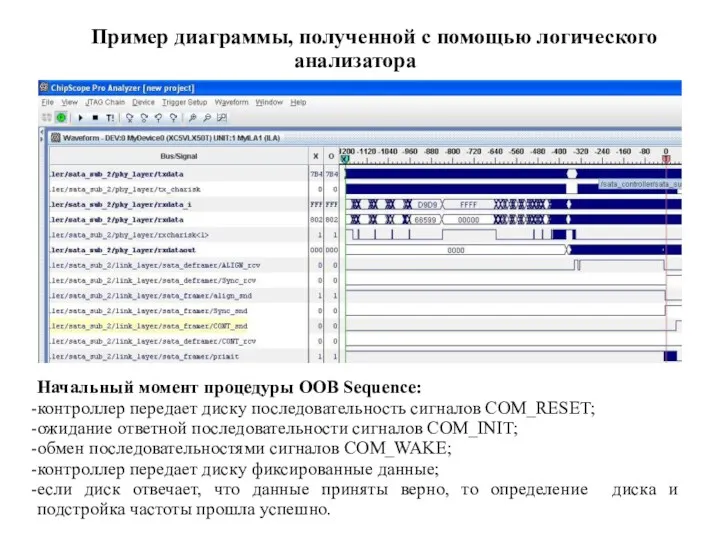

- 16. Пример диаграммы, полученной с помощью логического анализатора Начальный момент процедуры OOB Sequence: контроллер передает диску последовательность

- 17. Результаты: - разработано RTL-описание универсального SATA- IO-link контроллера с интерфейсами Legacy и AHCI; - получен макет

- 19. Скачать презентацию

Структура знаний и образовательных программ по информатике и компьютерным технологиям

Структура знаний и образовательных программ по информатике и компьютерным технологиям Задания международного конкурса по информатике - Бобёр 2013

Задания международного конкурса по информатике - Бобёр 2013 История вычислительной техники

История вычислительной техники Геинформационная система ГИС Панорама

Геинформационная система ГИС Панорама Перевод чисел из одной системы счисления в другую

Перевод чисел из одной системы счисления в другую Базы данных

Базы данных Презентация Microsoft PowerPoint (2)

Презентация Microsoft PowerPoint (2) Профессиография

Профессиография Створення лінійних алгоритмів

Створення лінійних алгоритмів презентация к уроку информатике 11 класс Информационные оптимизационные модели

презентация к уроку информатике 11 класс Информационные оптимизационные модели История развития вычислительной техники

История развития вычислительной техники Защита от несанкционированного доступа к информации

Защита от несанкционированного доступа к информации Ինֆորմատիկա

Ինֆորմատիկա Презентация по теме:Объекты и их свойства 3 класс

Презентация по теме:Объекты и их свойства 3 класс Программирование на Паскале - первый уровень. Простые (линейные) программы

Программирование на Паскале - первый уровень. Простые (линейные) программы Применение контрольно-кассовой техники в 2018 году. Операции по кассе

Применение контрольно-кассовой техники в 2018 году. Операции по кассе Информационные Системы

Информационные Системы Технологии проектирования информационных систем. Структурные модели предметной области

Технологии проектирования информационных систем. Структурные модели предметной области Типы, переменные, управляющие инструкции. Массивы. (Тема 2.5)

Типы, переменные, управляющие инструкции. Массивы. (Тема 2.5) Памятка пользователя Личного кабинета

Памятка пользователя Личного кабинета Инструкция по работе с сайтом ГМУ

Инструкция по работе с сайтом ГМУ Зимняя школа журналистики. Программа

Зимняя школа журналистики. Программа Создание и использование мультимедийных презентаций в начальной школе (курсовая работа)

Создание и использование мультимедийных презентаций в начальной школе (курсовая работа) Разработка информационного обеспечения для поддержки деятельности предприятия сферы услуг

Разработка информационного обеспечения для поддержки деятельности предприятия сферы услуг Перевод чисел из двоичной системы счисления в восьмеричную, шестнадцатеричную системы счисления

Перевод чисел из двоичной системы счисления в восьмеричную, шестнадцатеричную системы счисления Стилевое форматирование текста

Стилевое форматирование текста Augmented Reality and Project Glass

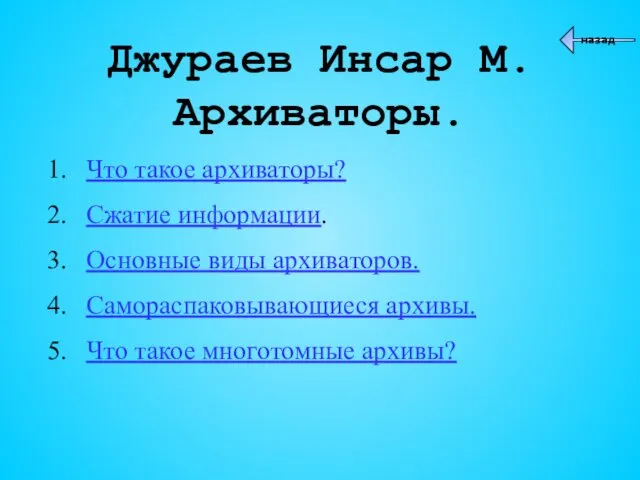

Augmented Reality and Project Glass Архиваторы

Архиваторы