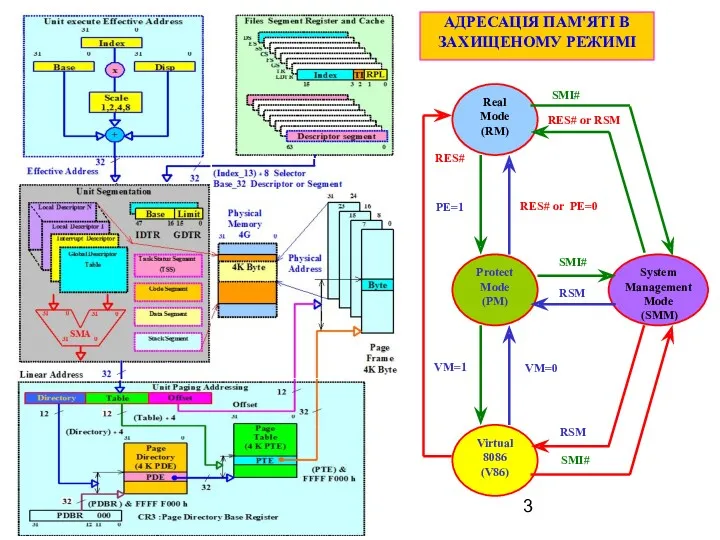

1 Адресація пам'яті в захищеному режимі……………………………………………………………..3

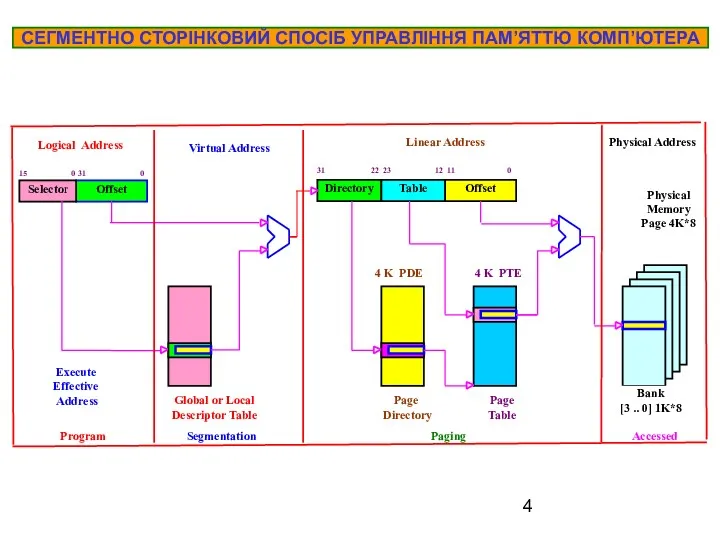

2 Сегментно сторінковий спосіб управління пам’яттю

комп’ютера………………………….4

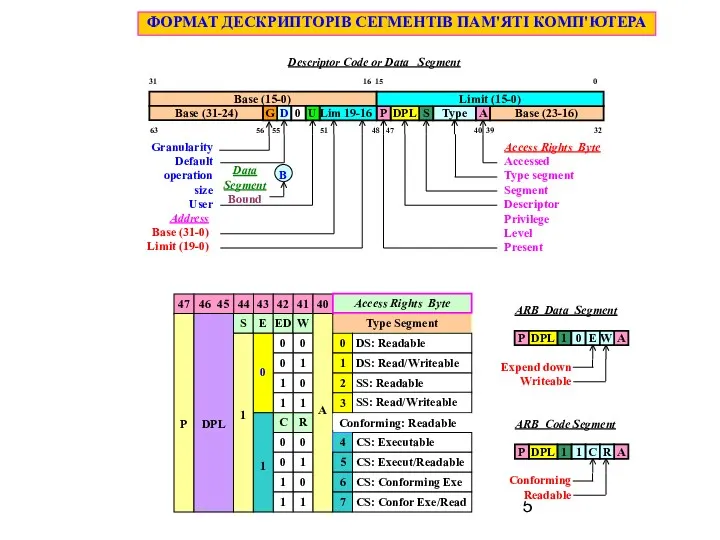

2 Формат дескрипторів сегментів пам'яті комп'ютера…………………………………………..5

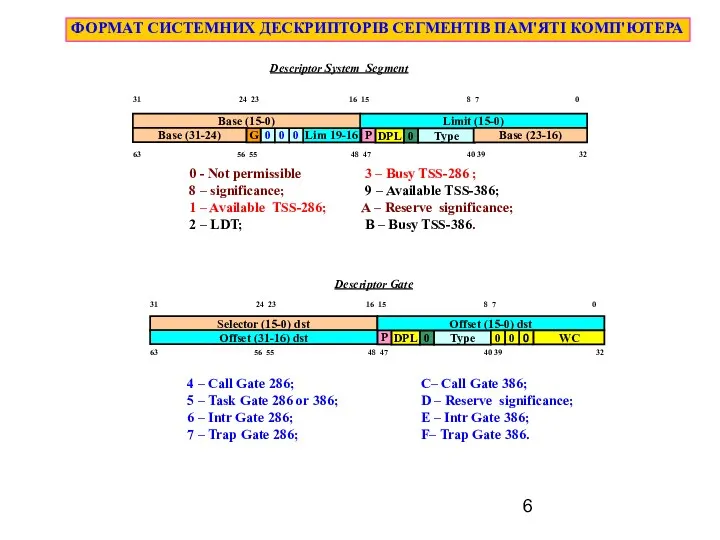

3 Формат системних дескрипторів сегментів пам'яті комп'ютера…………………………..6

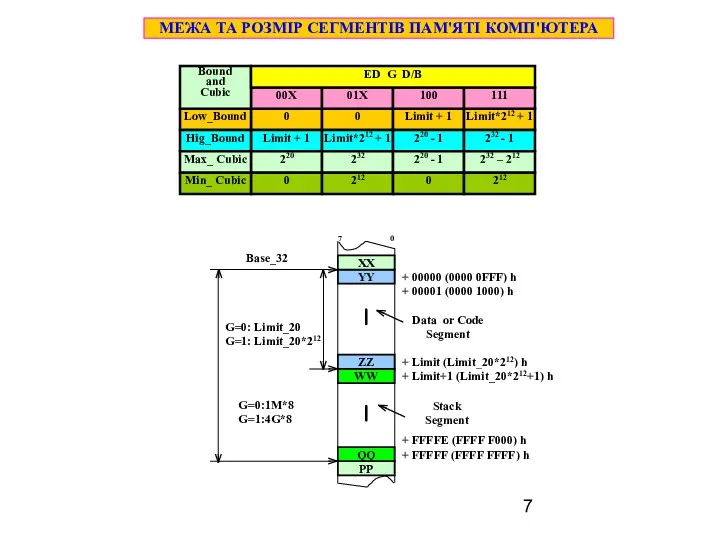

4 Межа та розмір сегментів пам'яті комп'ютера……………………………………………………7

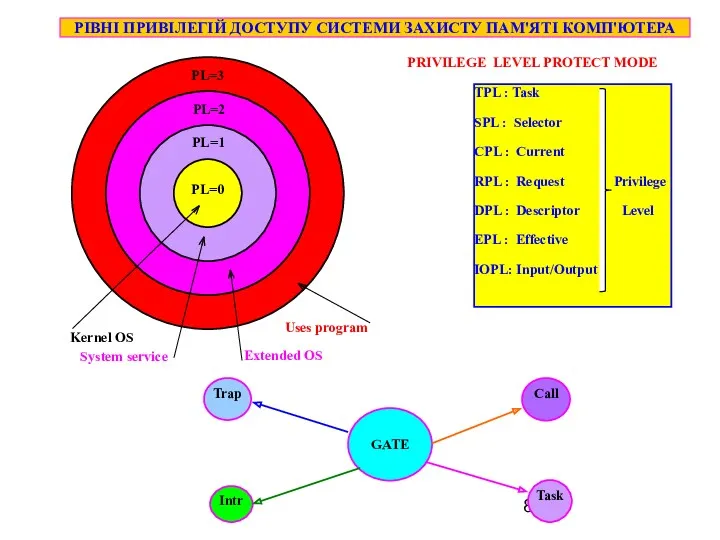

5 Рівні привілегій доступу системи захисту пам'яті комп'ютера……………………………..8

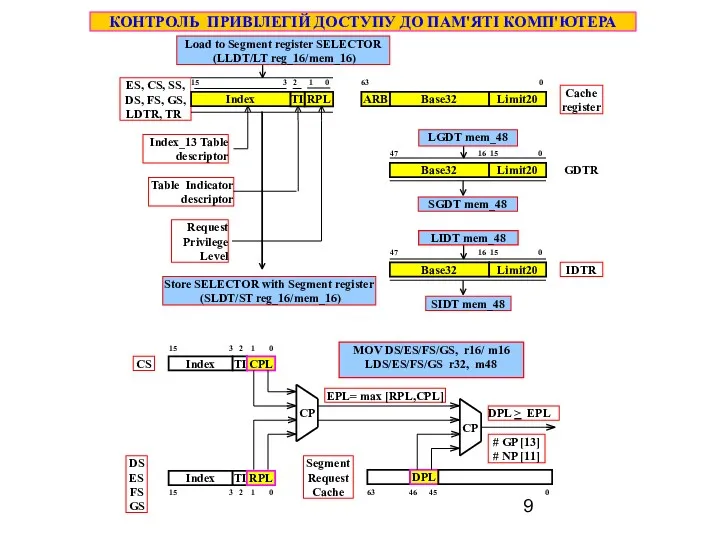

6 Контроль привілегій доступу до пам'яті комп'ютера…………………………………………..9

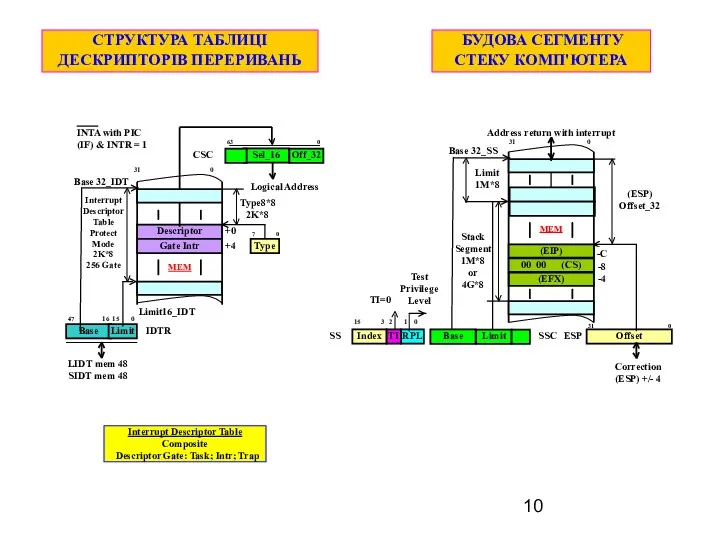

7 Структура таблиці дескрипторів переривань. Будова сегменту стеку комп'ютера..10

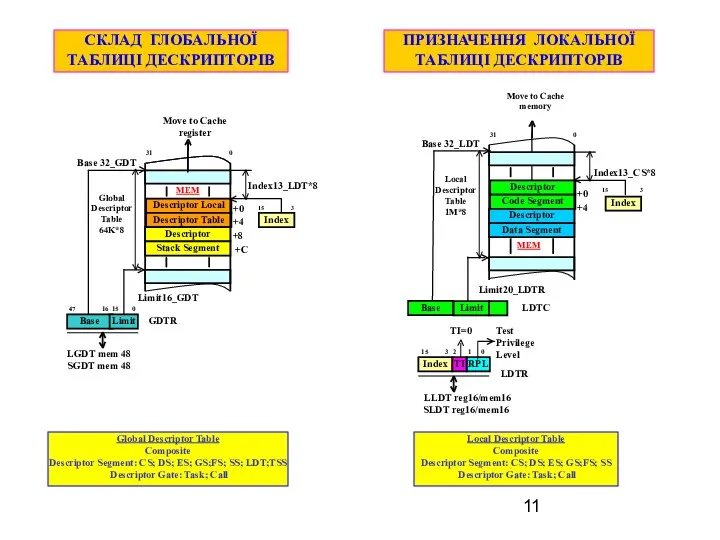

8 Склад глобальної таблиці дескрипторів. Призначення локальної таблиці

дескрипторів………………………………………………………………………………………………..11

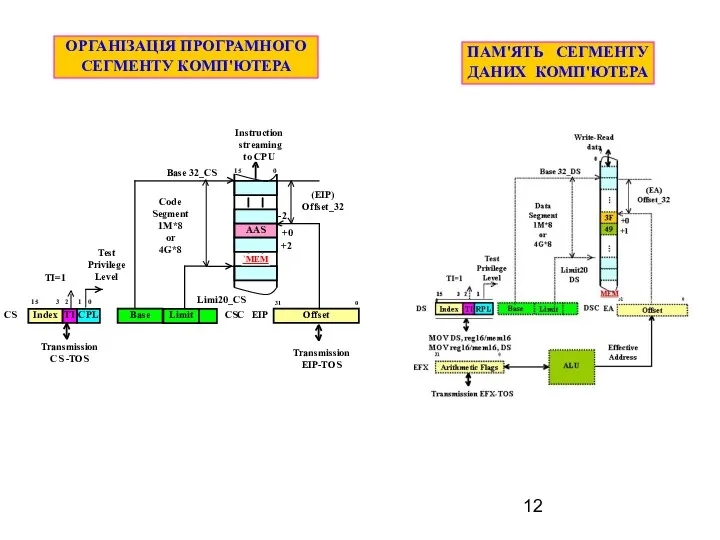

9 Організація програмного сегменту комп'ютера. Пам'ять сегменту даних комп'ютера………………………………………………………………………………………………….12

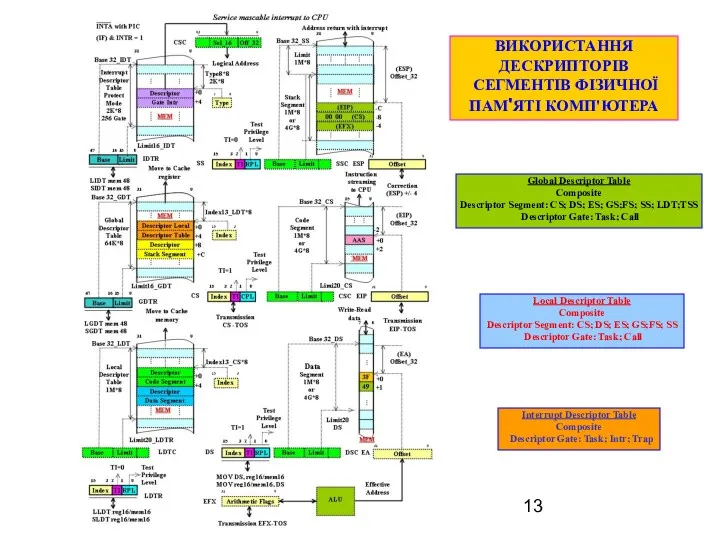

10 Використання дескрипторів. Сегментів фізичної пам'яті комп'ютера……………………13

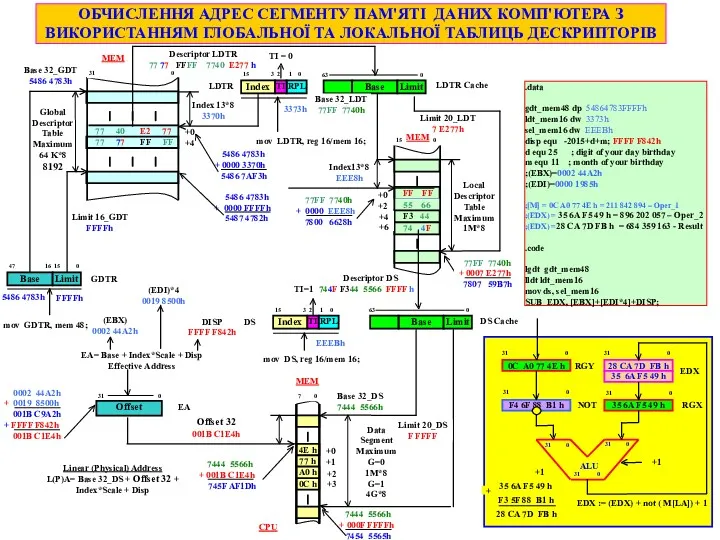

11 Обчислення адрес сегменту пам'яті даних комп'ютера з використанням

глобальної та локальної таблиць дескрипторів………………………………………………….14

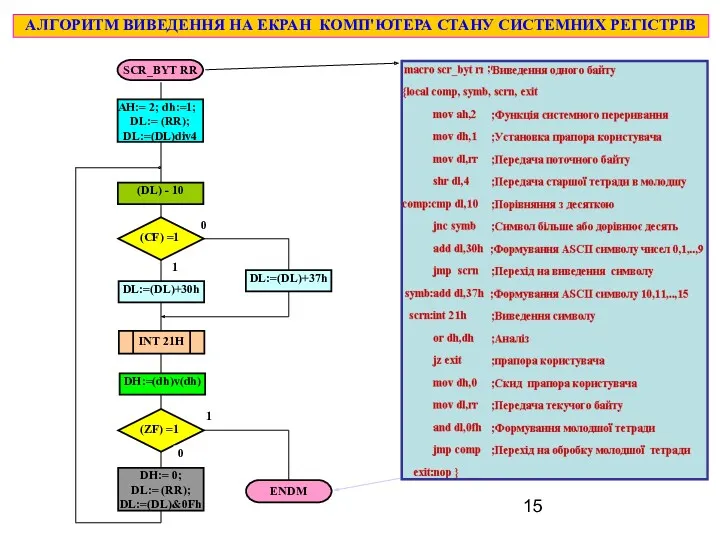

12 Алгоритм виведення на екран комп'ютера стану системних регістрів………………….15

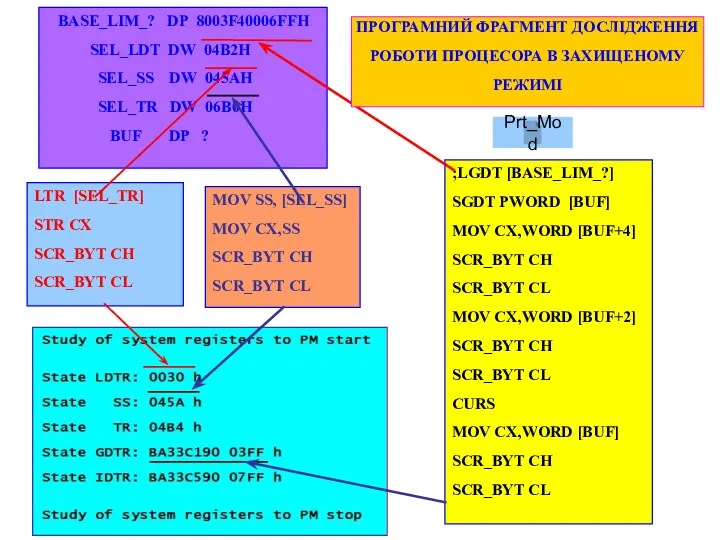

13 Програмний фрагмент дослідження роботи процесора в захищеному режимі………….16

ЗАХИЩЕНИЙ РЕЖИМ РОБОТИ ГОЛОВНОГО ПРОЦЕСОРА КОМП'ЮТЕРА

JavaScript. Lesson 6

JavaScript. Lesson 6 Классы и ключевые слова ООП. Лекция 7

Классы и ключевые слова ООП. Лекция 7 Моя будущая профессия - разработчик игр

Моя будущая профессия - разработчик игр Нормативно-правовое регулирование развития цифровой экономики в РФ

Нормативно-правовое регулирование развития цифровой экономики в РФ Финансовая отчетность для владельца бизнеса. 1С:Управление небольшой фирмой 8

Финансовая отчетность для владельца бизнеса. 1С:Управление небольшой фирмой 8 Информатика: предмет и задачи

Информатика: предмет и задачи All C# Operators by precendence

All C# Operators by precendence Испытания программного обеспечения средств измерений. Семинар

Испытания программного обеспечения средств измерений. Семинар Информационные ресурсы и сервисы интернета

Информационные ресурсы и сервисы интернета Определение и свойства алгоритмов

Определение и свойства алгоритмов Презентации к урокам. 11 класс Диск

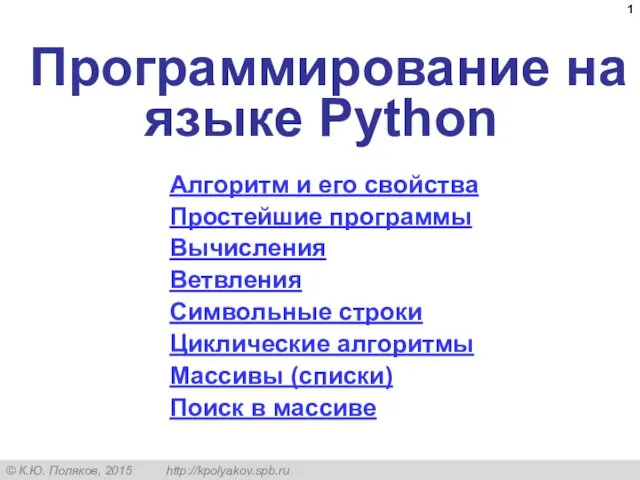

Презентации к урокам. 11 класс Диск Python 8

Python 8 Модели пространственных данных

Модели пространственных данных Решение задач ЕГЭ типа В2

Решение задач ЕГЭ типа В2 Сравнительный анализ применения сканирующих геодезических приборов

Сравнительный анализ применения сканирующих геодезических приборов Технология Drag and Drop

Технология Drag and Drop Проектирование и разработка информационной системы для управления движением материальных средств продуктовой оптовой базы

Проектирование и разработка информационной системы для управления движением материальных средств продуктовой оптовой базы Защита беспилотных летательных аппаратов от спуфинг атак

Защита беспилотных летательных аппаратов от спуфинг атак Виртуальные машины

Виртуальные машины Роль модульных сеток всех видов в создании унифицированной схемы верстки всей печатной продукции корпорации

Роль модульных сеток всех видов в создании унифицированной схемы верстки всей печатной продукции корпорации Что такое информация?

Что такое информация? Проектирование и разработка информационной системы учета заявлений работников на предприятии

Проектирование и разработка информационной системы учета заявлений работников на предприятии Mobile Legends

Mobile Legends Компьютерная графика и анимация

Компьютерная графика и анимация Памятка терминов и определений для детей и родителей Безопасный интернет

Памятка терминов и определений для детей и родителей Безопасный интернет Распечатка листов подбора. Печать этикеток. Распечатка актов приема - передачи

Распечатка листов подбора. Печать этикеток. Распечатка актов приема - передачи 47320

47320 Решение задачи оптимального планирования

Решение задачи оптимального планирования