Содержание

- 2. Представление информации физическими сигналами Представление цифровой информации сигналами потенциального типа (последовательный код). Представление информации параллельным кодом

- 3. КЛАССИФИКАЦИЯ ЦУ По способу ввода и вывода Устройства последовательностного действия Устройства параллельного действия Устройства смешанного действия

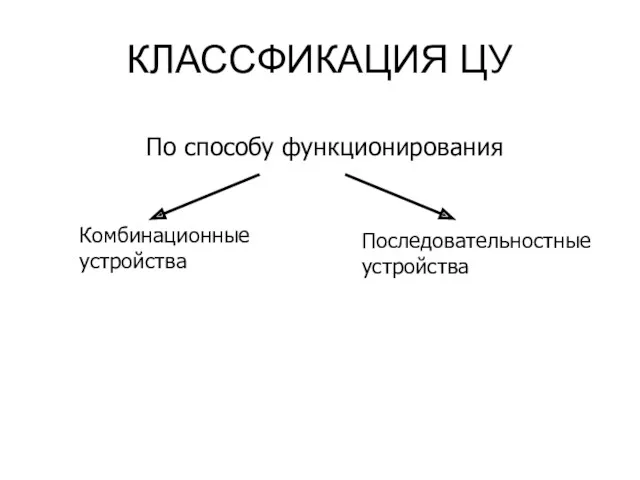

- 4. КЛАССФИКАЦИЯ ЦУ По способу функционирования Комбинационные устройства Последовательностные устройства

- 5. БУЛЕВА АЛГЕБРА СПОСОБЫ ЗАДАНИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ ТАБЛИЦА ИСТИННОСТИ БУЛЕВО ВЫРАЖЕНИЕ СХЕМА НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ

- 6. ТАБЛИЦА ИСТИННОСТИ

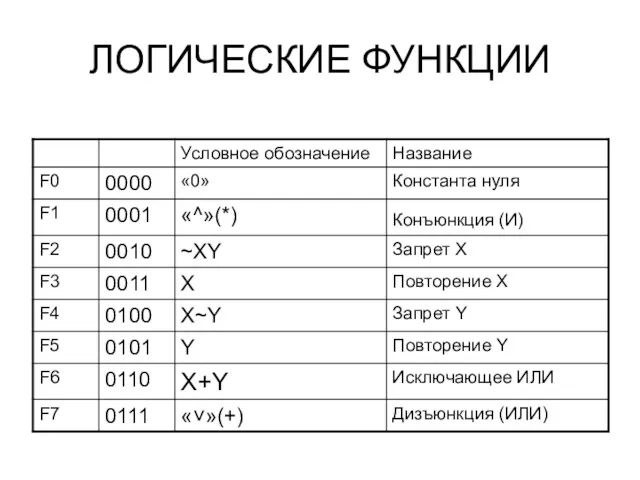

- 7. ЛОГИЧЕСКИЕ ФУНКЦИИ

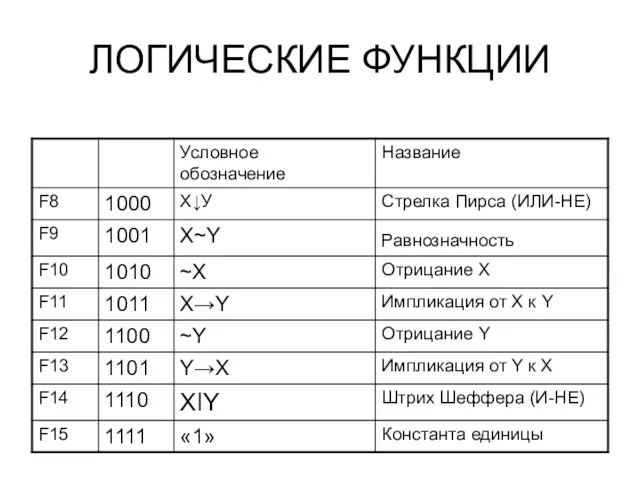

- 8. ЛОГИЧЕСКИЕ ФУНКЦИИ

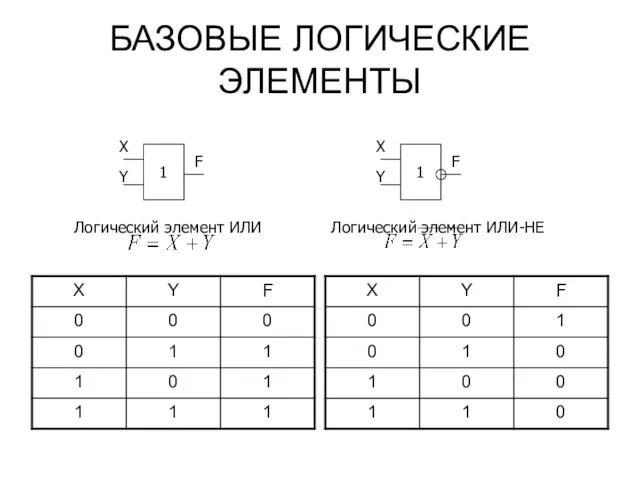

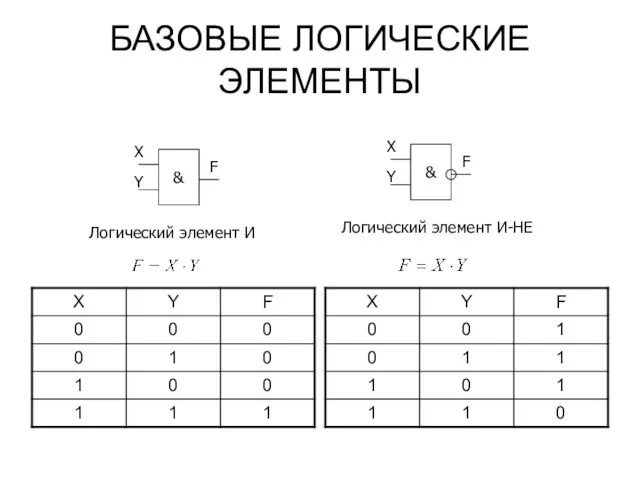

- 9. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

- 10. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

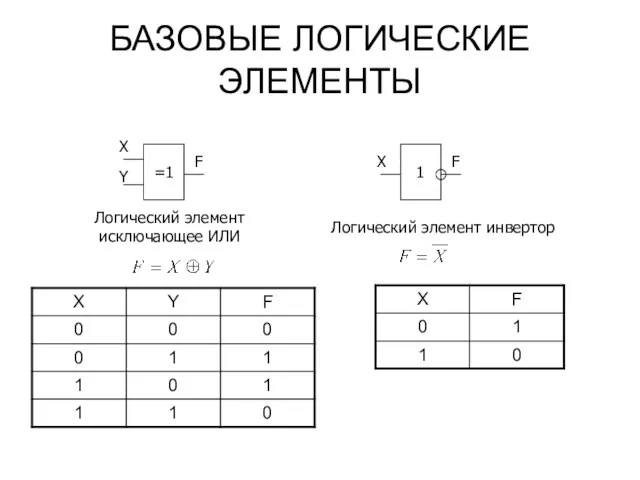

- 11. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ Логический элемент исключающее ИЛИ 1 Х F Логический элемент инвертор

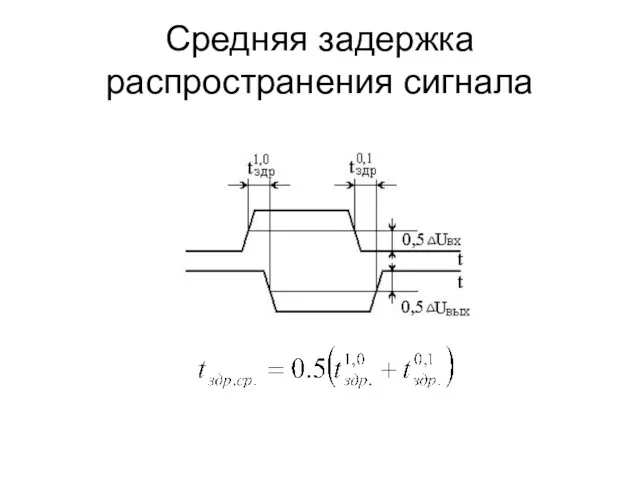

- 12. Средняя задержка распространения сигнала

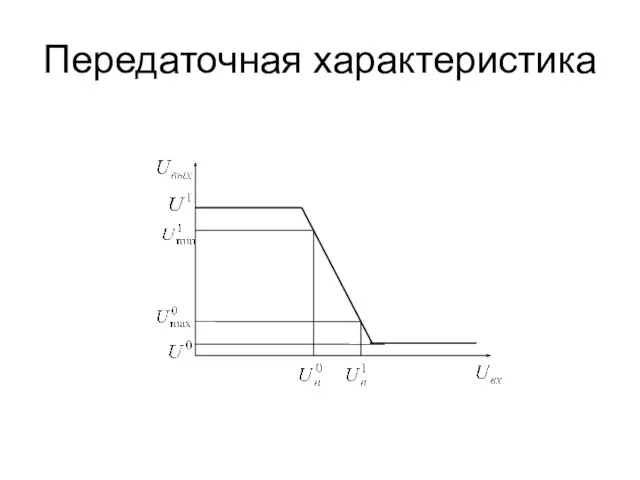

- 13. Передаточная характеристика

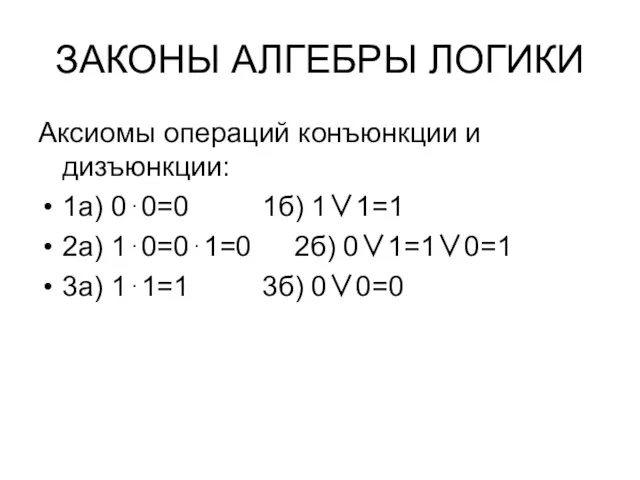

- 14. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ Аксиомы операций конъюнкции и дизъюнкции: 1а) 0⋅0=0 1б) 1∨1=1 2а) 1⋅0=0⋅1=0 2б) 0∨1=1∨0=1

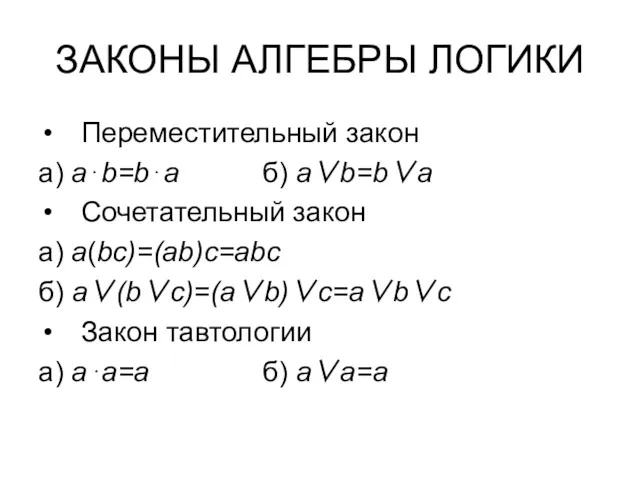

- 15. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ Переместительный закон а) a⋅b=b⋅a б) a∨b=b∨a Сочетательный закон а) a(bc)=(ab)c=abc б) a∨(b∨c)=(a∨b)∨c=a∨b∨c Закон

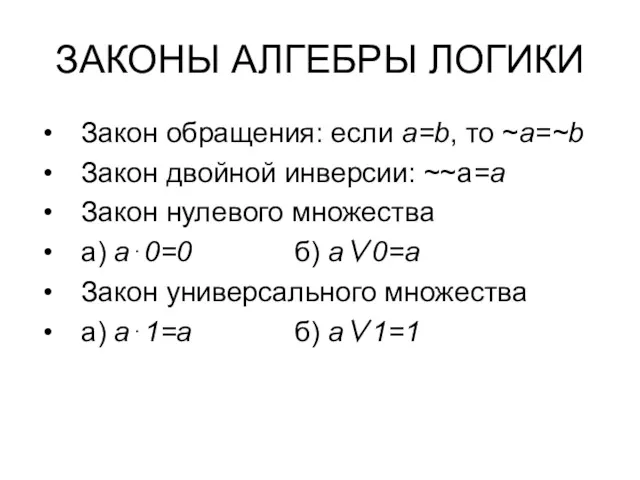

- 16. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ Закон обращения: если a=b, то ~a=~b Закон двойной инверсии: ~~a=a Закон нулевого множества

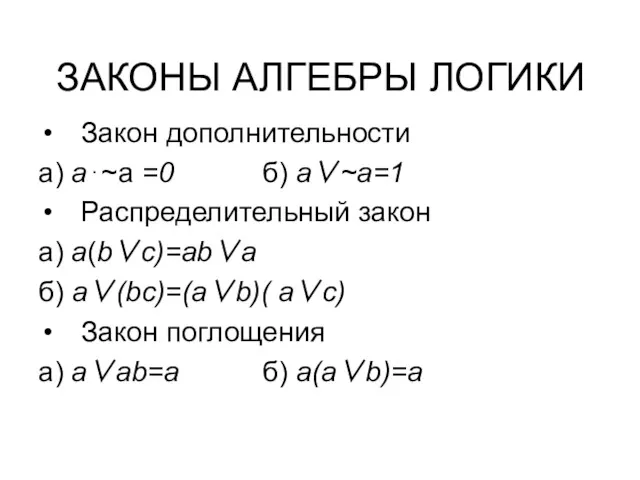

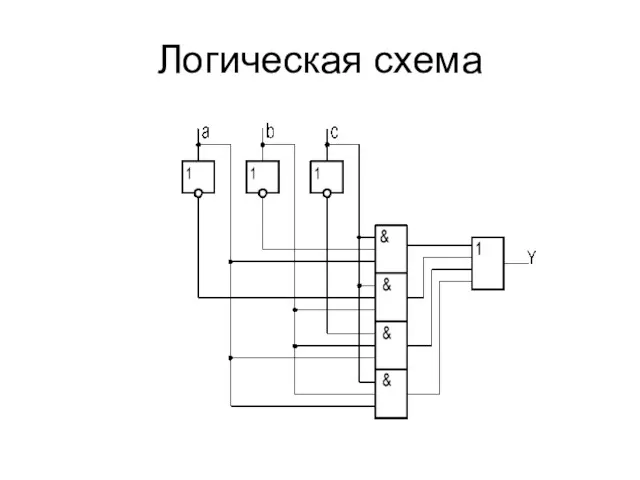

- 17. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ Закон дополнительности а) a⋅~a =0 б) a∨~a=1 Распределительный закон а) a(b∨c)=ab∨a б) a∨(bc)=(a∨b)(

- 18. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ Закон склеивания а) (a∨b)(a∨~b)=a б) a*b∨ a*~b=a Закон инверсии (закон Де Моргана) а)

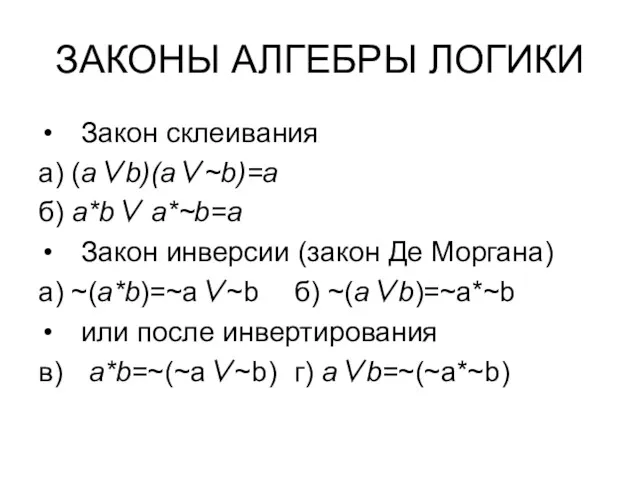

- 19. Произвольные функции и логические схемы

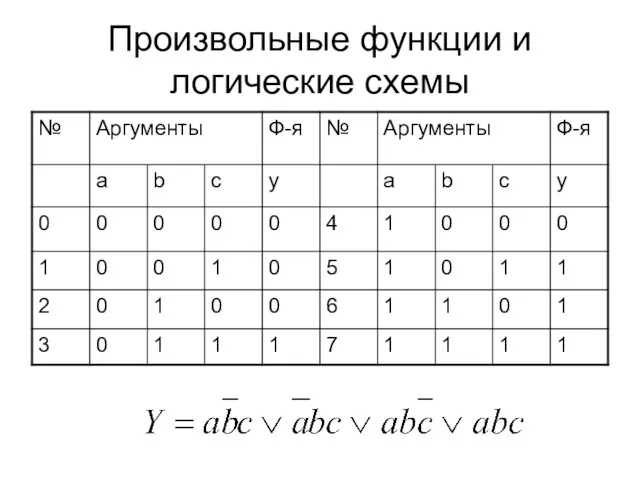

- 20. Логическая схема

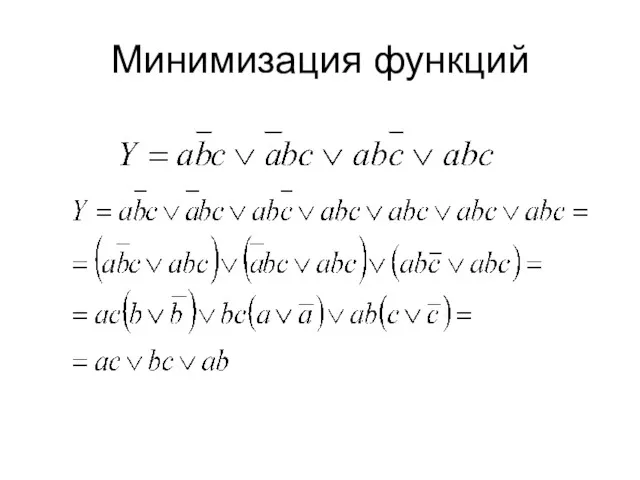

- 21. Минимизация функций

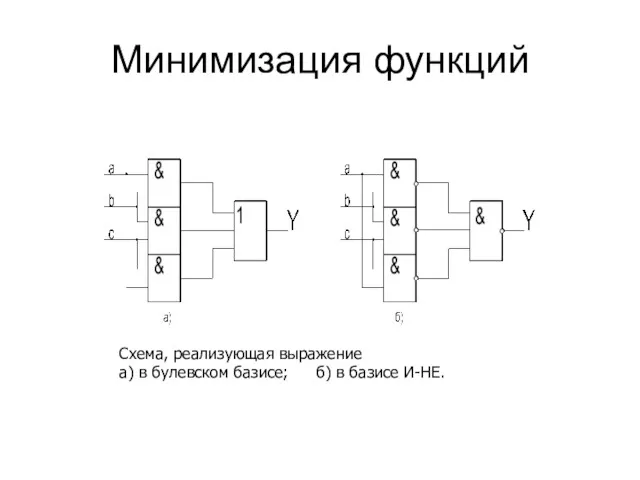

- 22. Минимизация функций Схема, реализующая выражение а) в булевском базисе; б) в базисе И-НЕ.

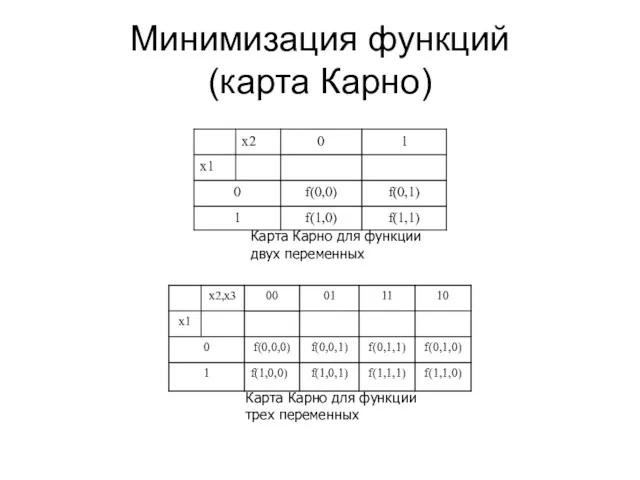

- 23. Минимизация функций (карта Карно) Карта Карно для функции двух переменных Карта Карно для функции трех переменных

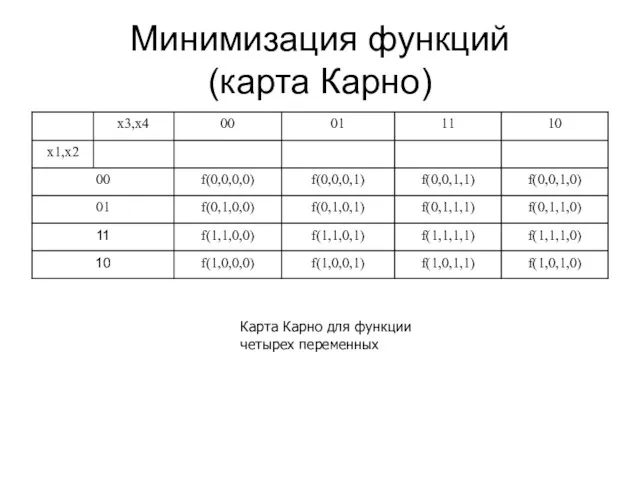

- 24. Минимизация функций (карта Карно) Карта Карно для функции четырех переменных

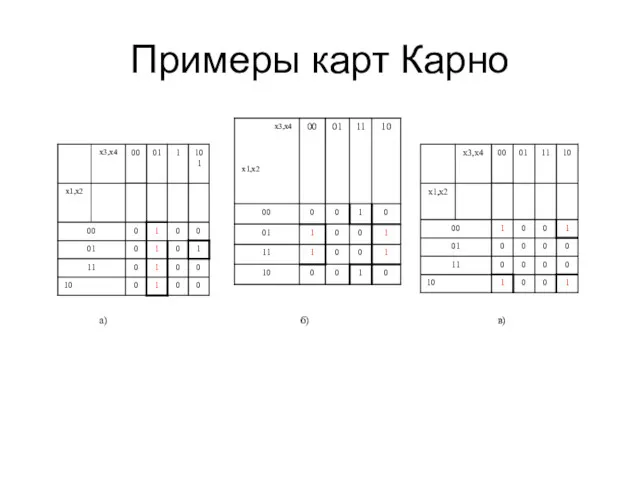

- 25. Примеры карт Карно а) б) в)

- 26. Типовые комбинационные устройства преобразователи кодов; коммутаторы; арифметические устройства; постоянные запоминающие устройства (ПЗУ).

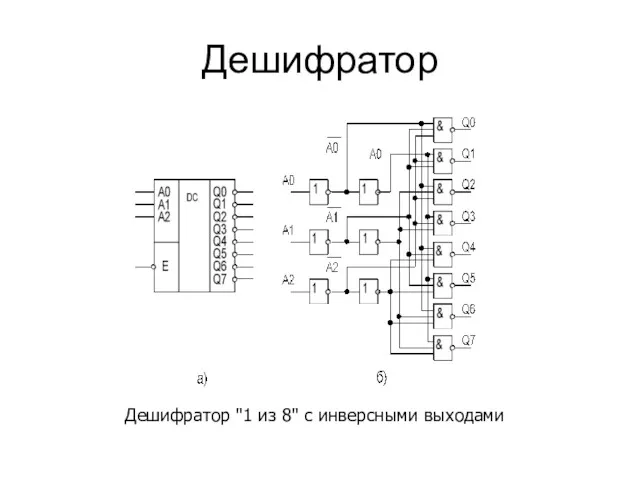

- 27. Дешифратор Дешифратор "1 из 8" с инверсными выходами

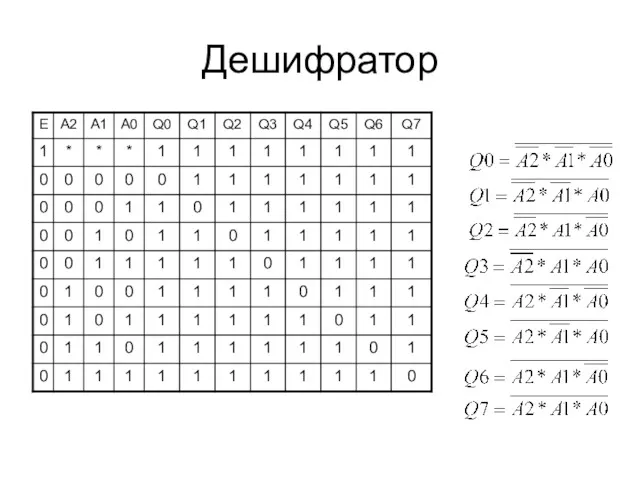

- 28. Дешифратор

- 29. Каскадное соединение дешифраторов

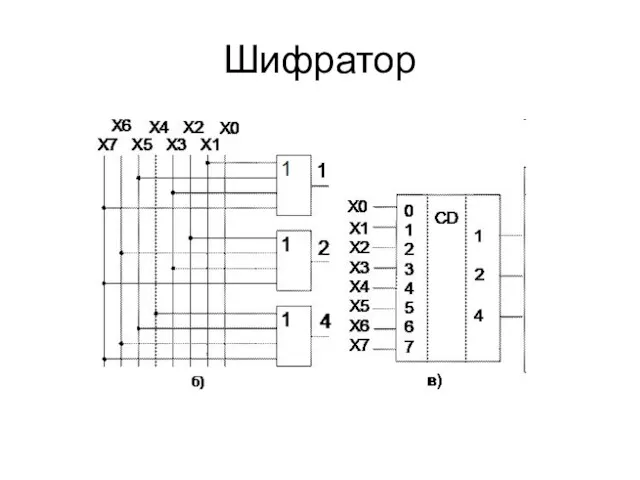

- 30. Шифратор

- 31. Шифратор

- 32. Приоритетный шифратор

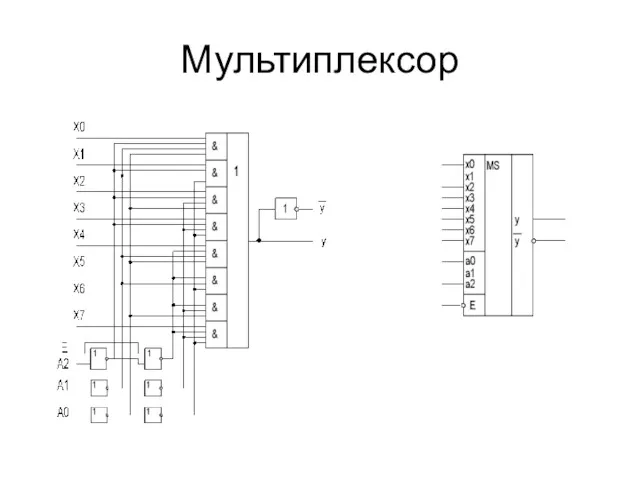

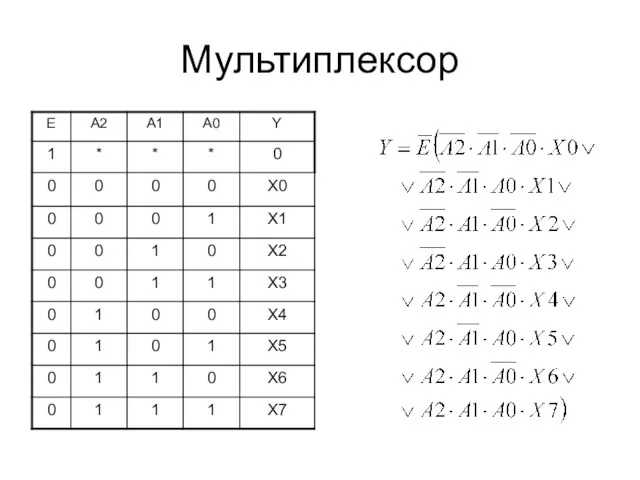

- 33. Мультиплексор

- 34. Мультиплексор

- 35. Наращивание мультиплексоров Мультиплексор К155КП1 а) и 32-входовой мультиплексор б)

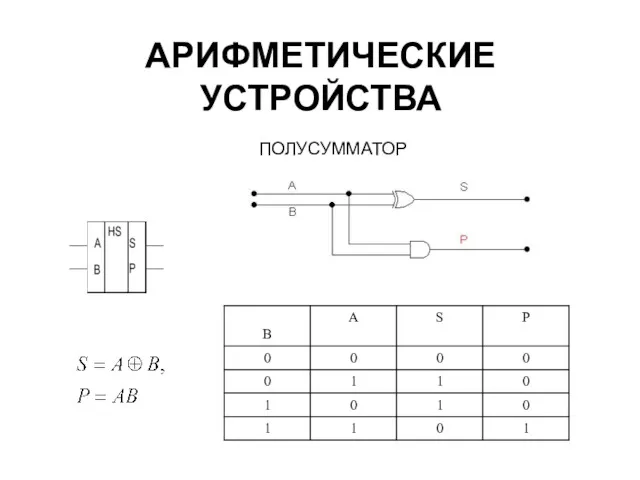

- 36. АРИФМЕТИЧЕСКИЕ УСТРОЙСТВА ПОЛУСУММАТОР

- 37. Сумматор

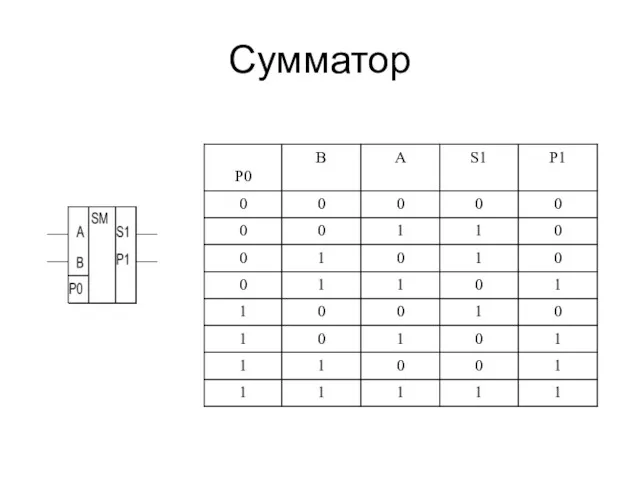

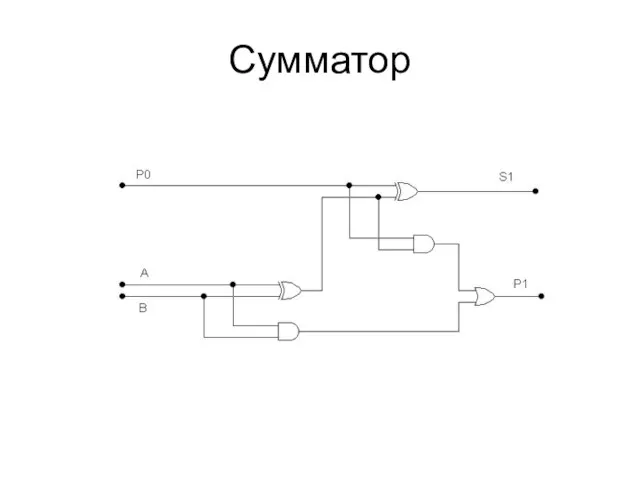

- 38. Сумматор

- 39. Сумматор с последовательным переносом

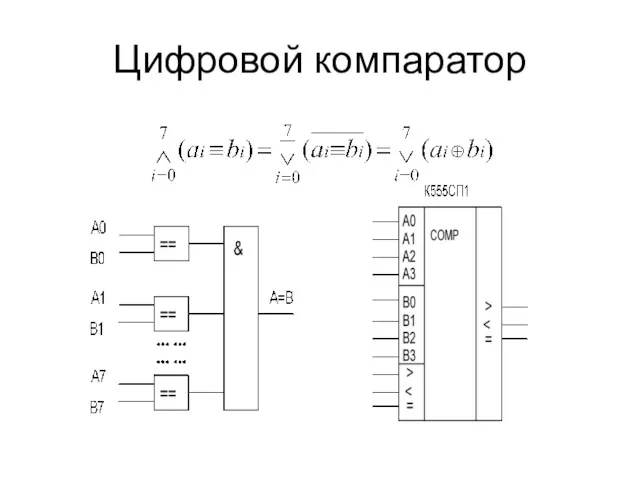

- 40. Цифровой компаратор

- 41. Контроль четности К примеру, в числе 0111 число единиц нечетно. 00111 - нечетный паритет; 10111 -

- 42. Контроль четности Условное изображение микросхемы К155ИП2.

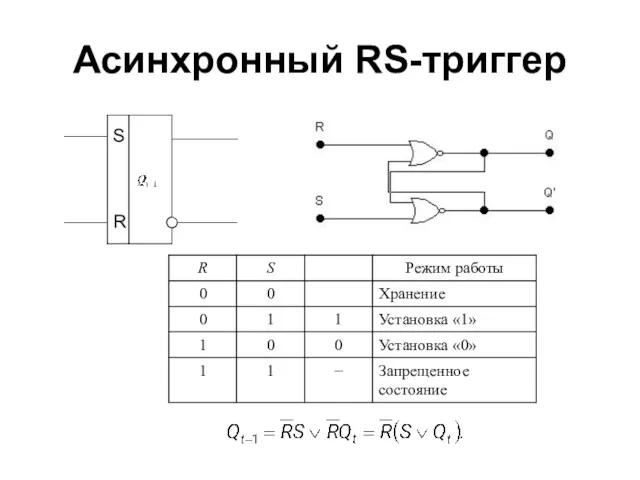

- 43. Асинхронный RS-триггер

- 44. Асинхронный RS-триггер с инверсными входами

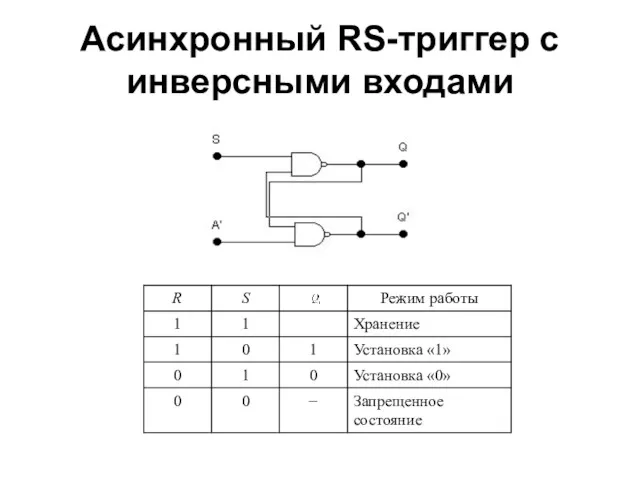

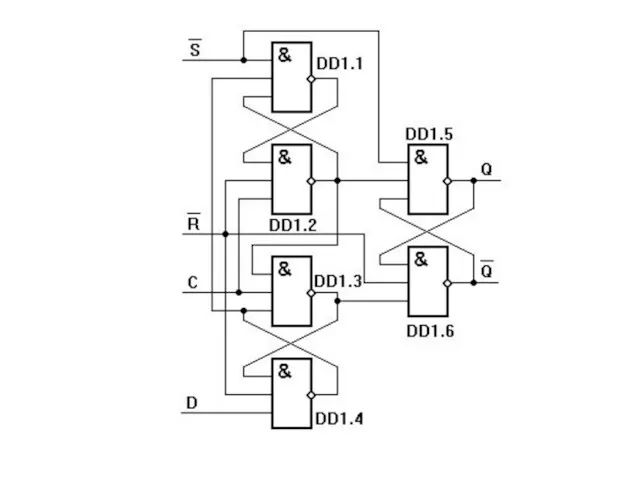

- 45. Синхронный RS-триггер

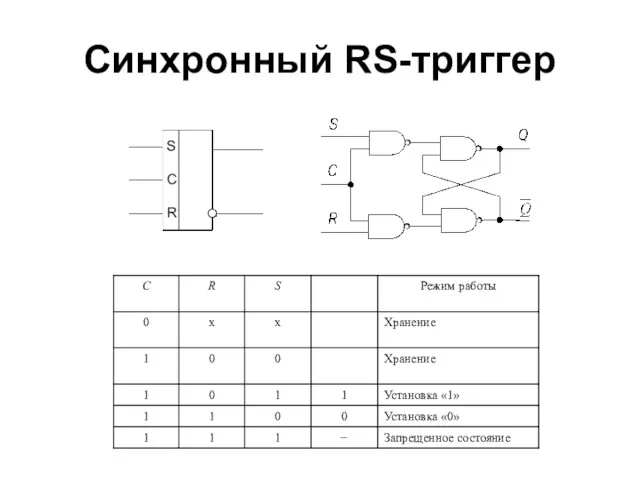

- 46. JK-триггер

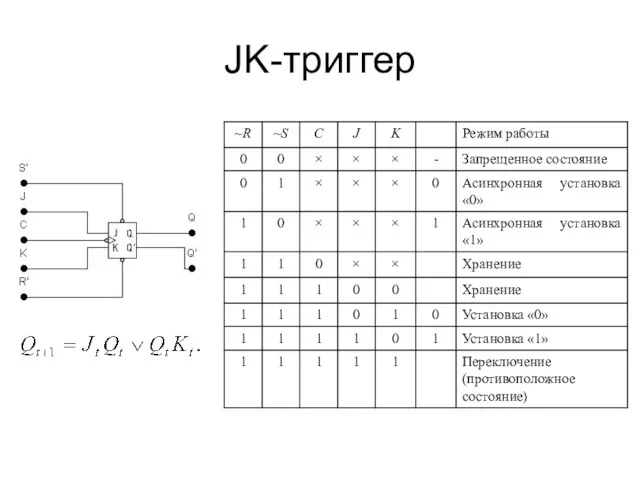

- 47. D-триггер

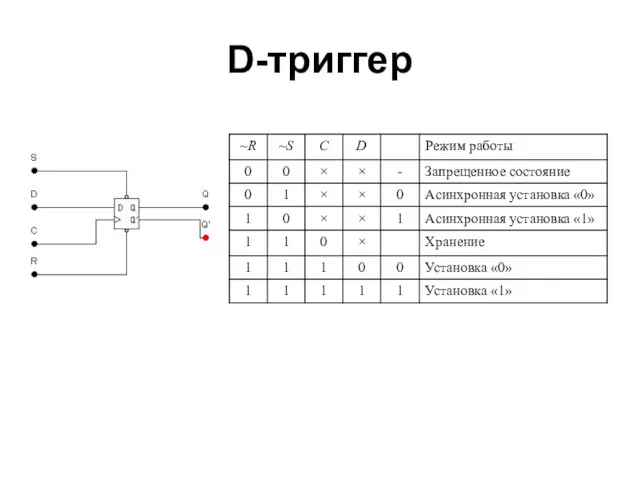

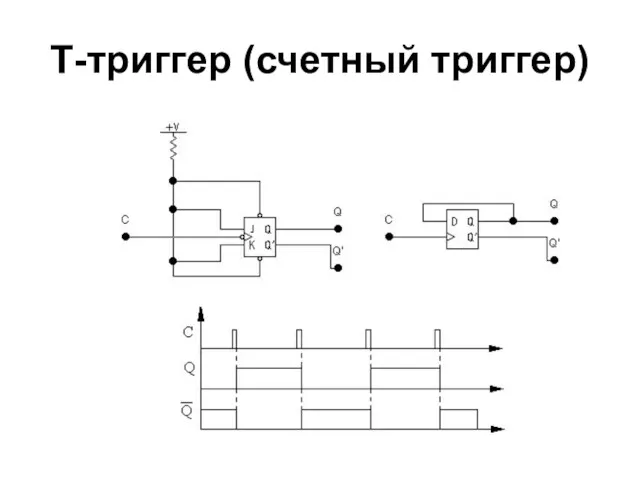

- 49. Т-триггер (счетный триггер)

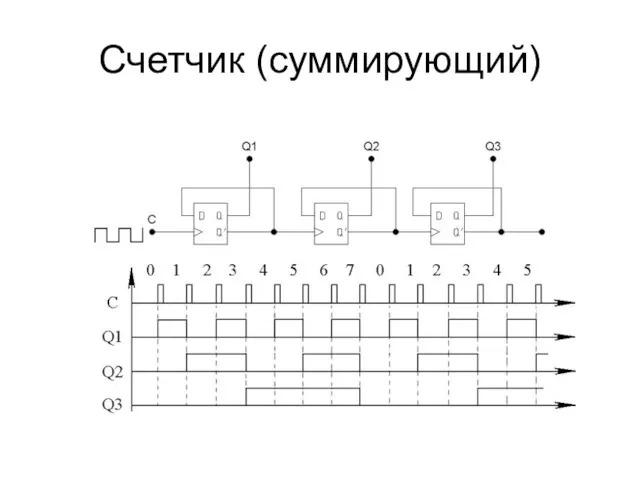

- 50. Счетчик (суммирующий)

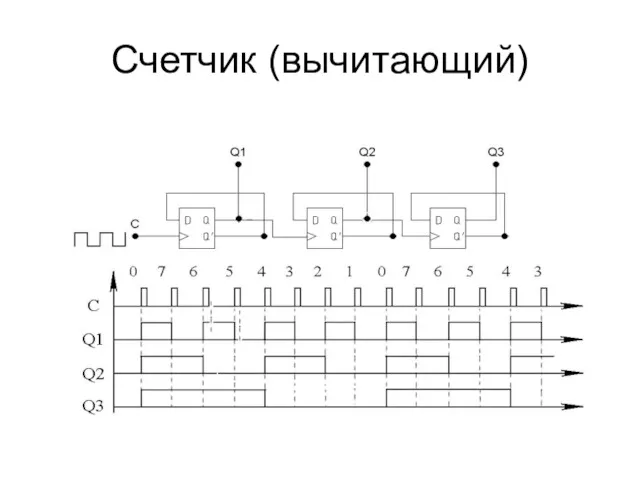

- 51. Счетчик (вычитающий)

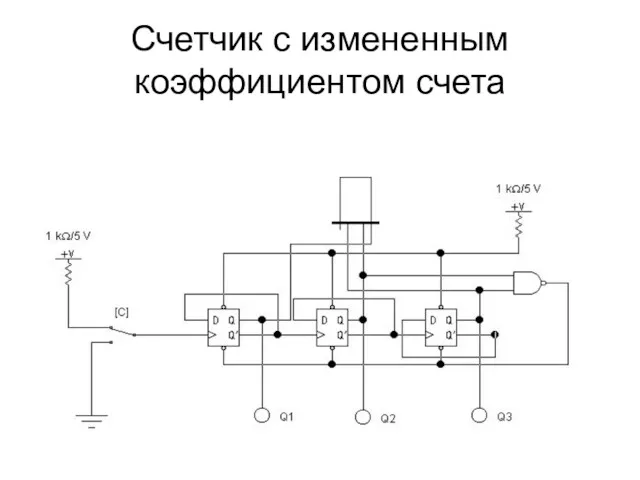

- 52. Счетчик с измененным коэффициентом счета

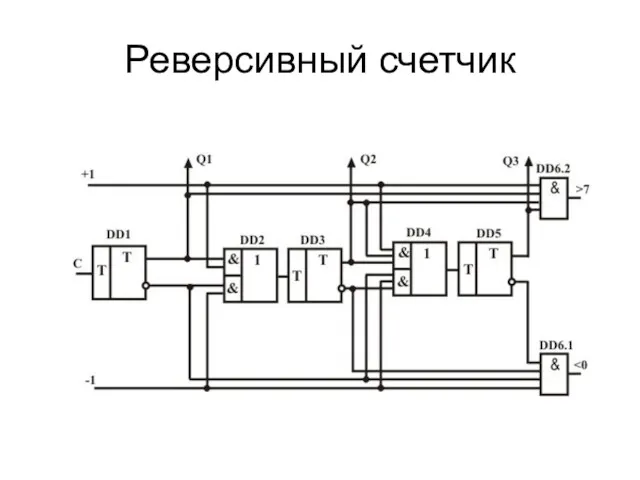

- 53. Реверсивный счетчик

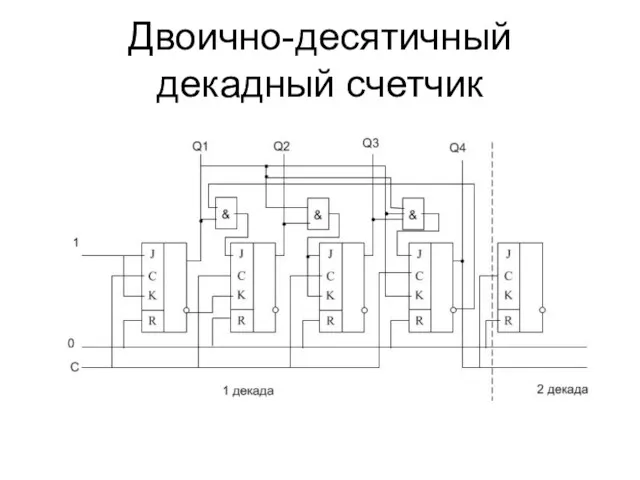

- 54. Двоично-десятичный декадный счетчик

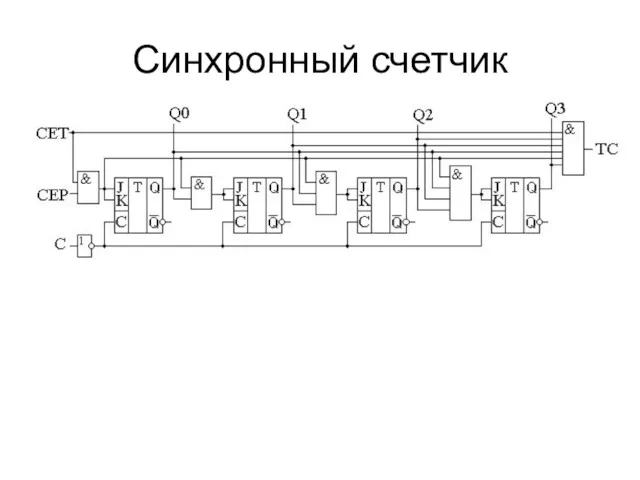

- 55. Синхронный счетчик

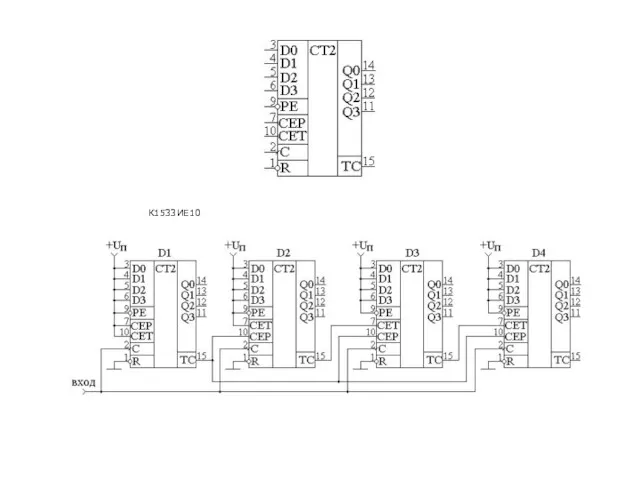

- 56. К1533ИЕ10

- 57. Делители частоты N=5

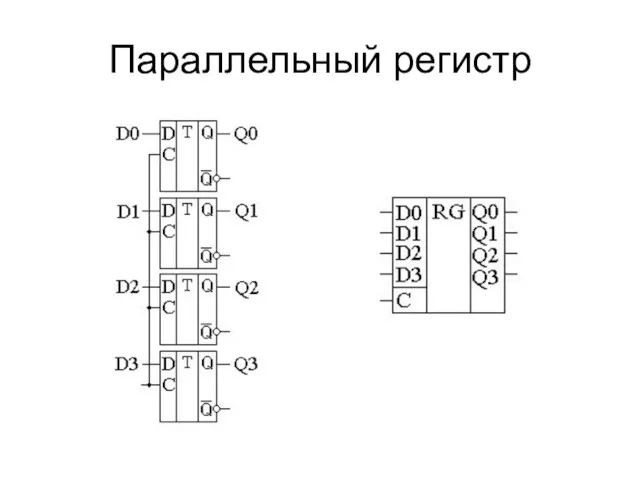

- 58. Параллельный регистр

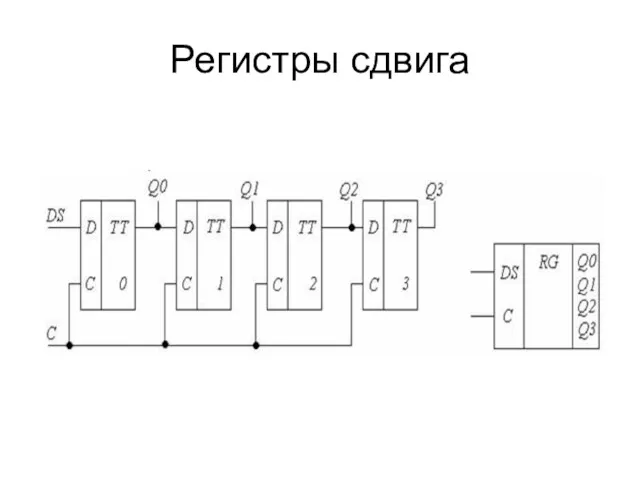

- 59. Регистры сдвига

- 60. Реверсивные регистры сдвига

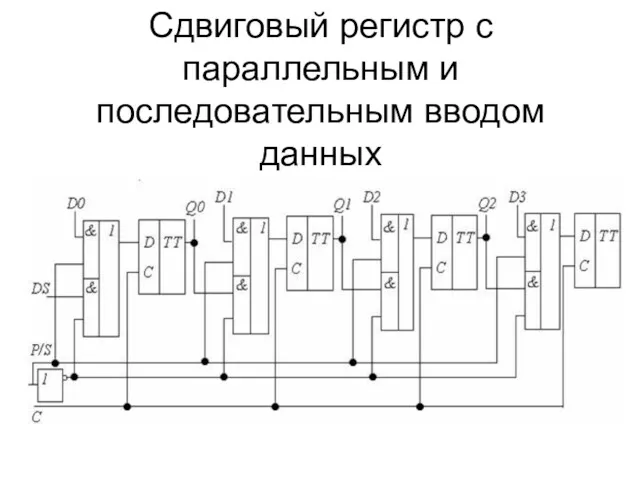

- 61. Сдвиговый регистр с параллельным и последовательным вводом данных

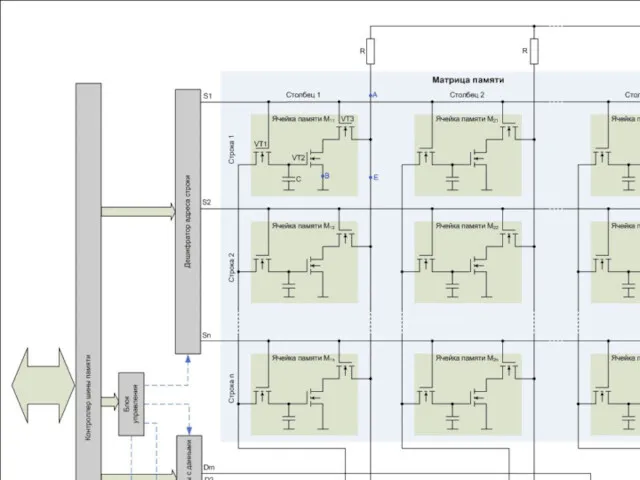

- 62. Типы ОЗУ 1. Динамическая память (DRAM) – энергозависимая полупроводниковая память с произвольным доступом, в которой каждый

- 63. Перспективные разработки ОЗУ - FRAM (Ferroelectric Random Access Memory) – сегнетоэлектрическая память, основывающаяся на сегнетоэлектриках –

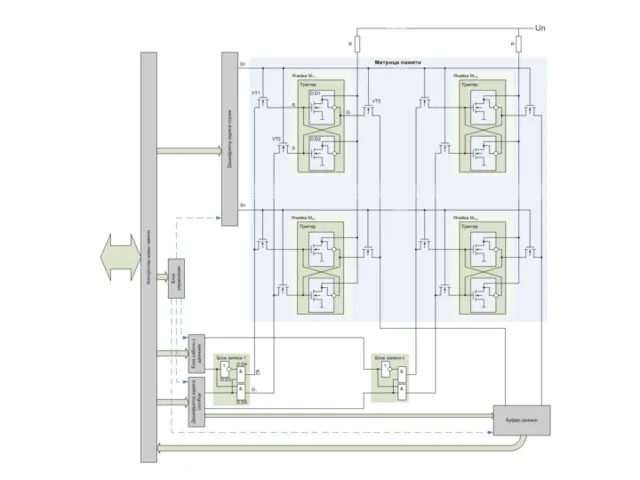

- 64. Устройство ячейки статической памяти

- 66. Достоинства и недостатки статической памяти Достоинства: высокая скорость работы; нет необходимости регенерации ячеек. Недостатки: высокая цена;

- 67. Устройство динамической оперативной памяти (DRAM – Dynamic Random Access Memory)

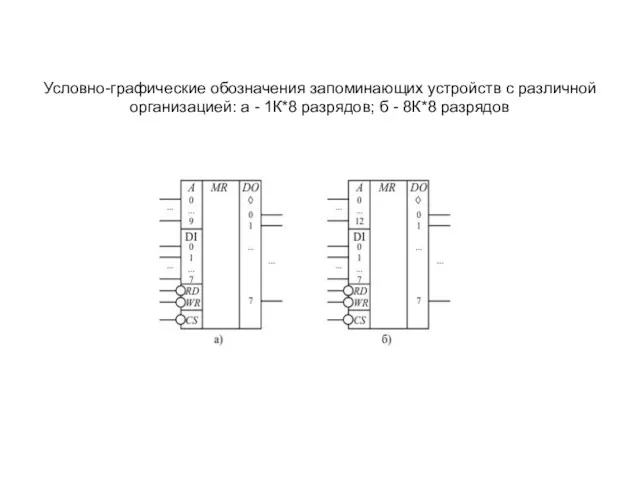

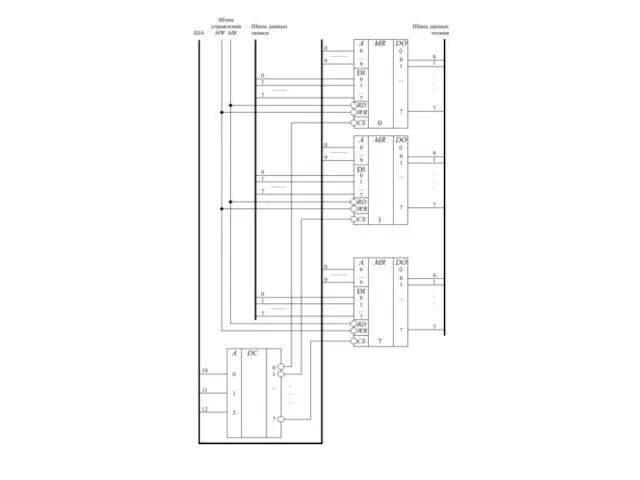

- 69. Условно-графические обозначения запоминающих устройств с различной организацией: а - 1К*8 разрядов; б - 8К*8 разрядов

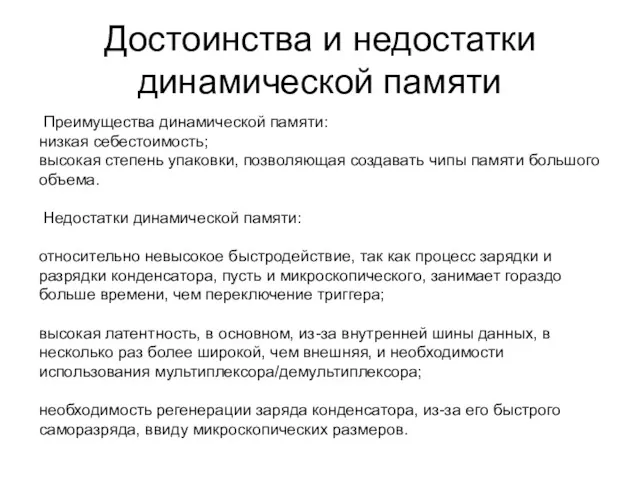

- 71. Достоинства и недостатки динамической памяти Преимущества динамической памяти: низкая себестоимость; высокая степень упаковки, позволяющая создавать чипы

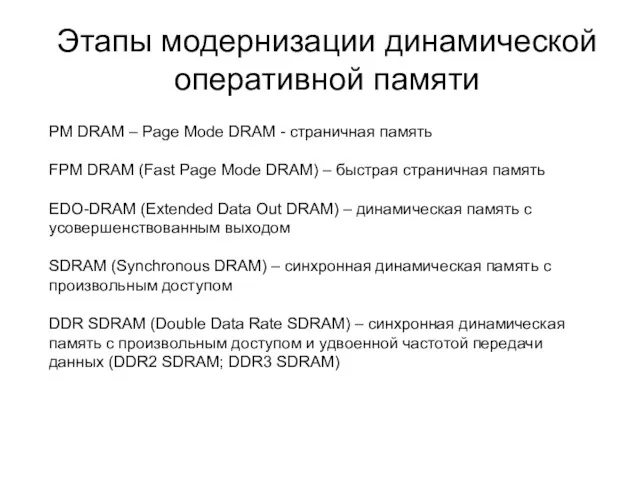

- 72. Этапы модернизации динамической оперативной памяти PM DRAM – Page Mode DRAM - страничная память FPM DRAM

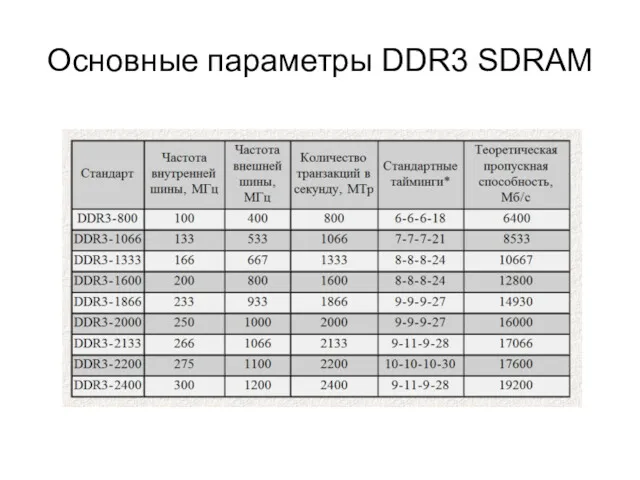

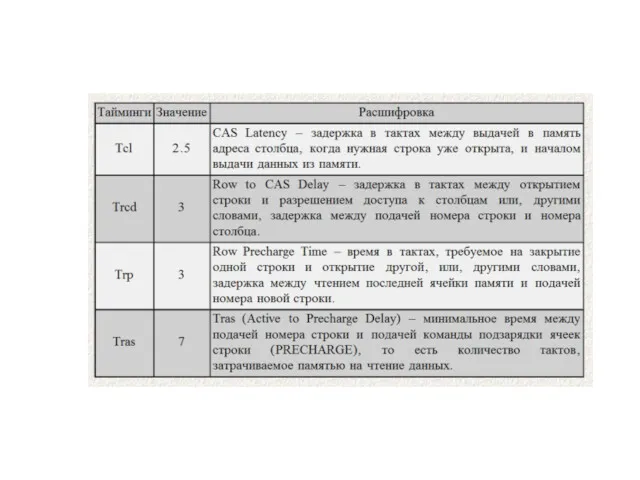

- 73. Основные параметры DDR3 SDRAM

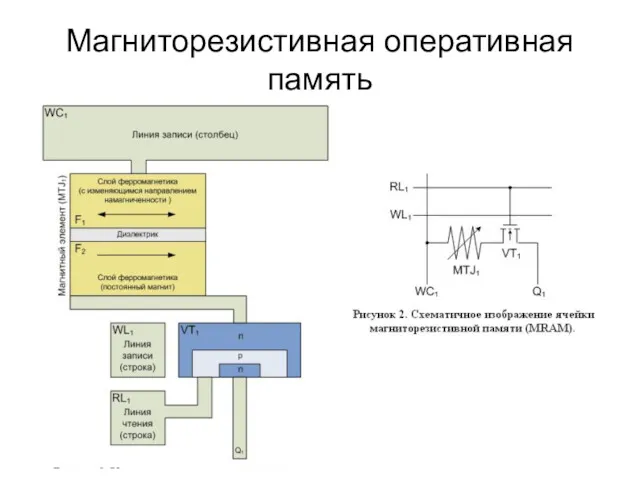

- 75. Магниторезистивная оперативная память

- 77. Скачать презентацию

7 класс, урок Устройства ввода-вывода

7 класс, урок Устройства ввода-вывода Особенности программирования на GPU

Особенности программирования на GPU Уведення та вставлення текстів на слайдах. Редагування і форматування текстів на слайдах. Урок №16. 5 клас

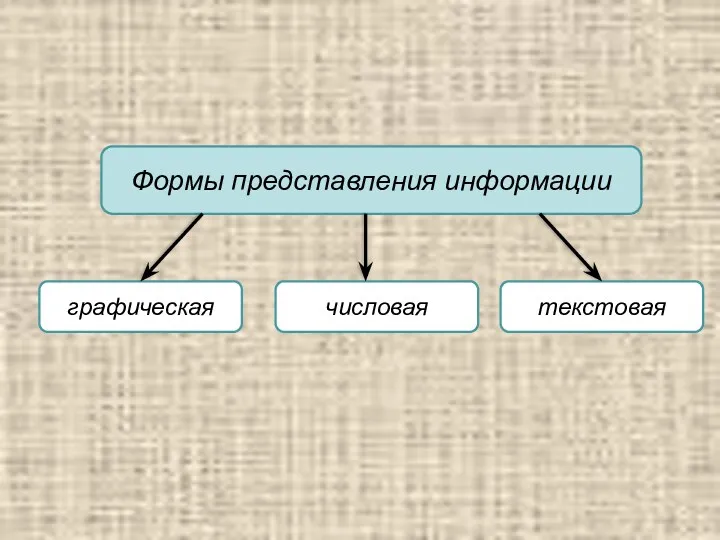

Уведення та вставлення текстів на слайдах. Редагування і форматування текстів на слайдах. Урок №16. 5 клас Действия с информацией

Действия с информацией Принципы обработки информации компьютером. Алгоритмы и способы их описания

Принципы обработки информации компьютером. Алгоритмы и способы их описания Основы работы в системе управления базами данных (СУБД) MS Access

Основы работы в системе управления базами данных (СУБД) MS Access Сетевой этикет

Сетевой этикет Средства массовой информации

Средства массовой информации Урок в 5 классе по теме Табличная форма представления информации

Урок в 5 классе по теме Табличная форма представления информации Программирование на С++. Функции

Программирование на С++. Функции Условный оператор в Паскале. 9 класс

Условный оператор в Паскале. 9 класс Краткая инструкция о том, как за 1 час поставить себе цель и сдвинуться с мёртвой точки

Краткая инструкция о том, как за 1 час поставить себе цель и сдвинуться с мёртвой точки Электронная библиотека издательства ЮРАЙТ. Общие сведения

Электронная библиотека издательства ЮРАЙТ. Общие сведения Цифровая схемотехника и архитектура компьютера. Микроархитектура. (Глава 7)

Цифровая схемотехника и архитектура компьютера. Микроархитектура. (Глава 7) Подход к решению задачи 27 Обработка строк

Подход к решению задачи 27 Обработка строк Facebook - социальная сеть

Facebook - социальная сеть A Display Model and Graphics Classes

A Display Model and Graphics Classes Кодирование текстовой информации. Представление информации в компьютере

Кодирование текстовой информации. Представление информации в компьютере Кибербуллинг: как помочь ребенку в ситуации онлайн-травли

Кибербуллинг: как помочь ребенку в ситуации онлайн-травли Компьютерные сети, Интернет и мультимедиа технологии. Архитектура сетей

Компьютерные сети, Интернет и мультимедиа технологии. Архитектура сетей Сеть поисковых систем Google

Сеть поисковых систем Google Задание правил проектирования для печатных плат

Задание правил проектирования для печатных плат презентация к уроку информатики в 9 классе.

презентация к уроку информатики в 9 классе. Применение электронных ресурсов при проведении уроков информатики

Применение электронных ресурсов при проведении уроков информатики О группе Однажды в сказке/ Once Upon A Time

О группе Однажды в сказке/ Once Upon A Time Компьютерная игра Tower Defense

Компьютерная игра Tower Defense Что такое Dota 2?

Что такое Dota 2? Аналіз впливу збільшення розмірності задачі на довжину паралельного упорядкування

Аналіз впливу збільшення розмірності задачі на довжину паралельного упорядкування