Содержание

- 2. Роль и место булевой алгебры Последовательность действий синтеза вычислительных устройств: Словесное описание функции Таблица истинности Алгебраическое

- 3. Последовательность действий в аппаратной среде Физико-технический процесс Транзистор Вентиль Узел Блок Устройство

- 4. Минимизация алгебраического выражения Минимизация алгебраического выражения проводится по двум критериям: Минимум аппаратных затрат (вентилей) Минимум времени

- 5. Законы Булевой алгебры Законы эквивалентности X + 1 = 1 X + 0 = X X

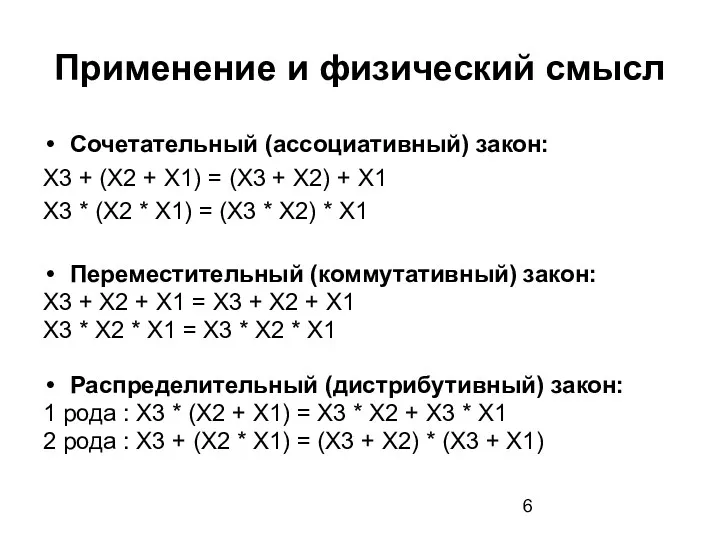

- 6. Применение и физический смысл Сочетательный (ассоциативный) закон: X3 + (X2 + X1) = (X3 + X2)

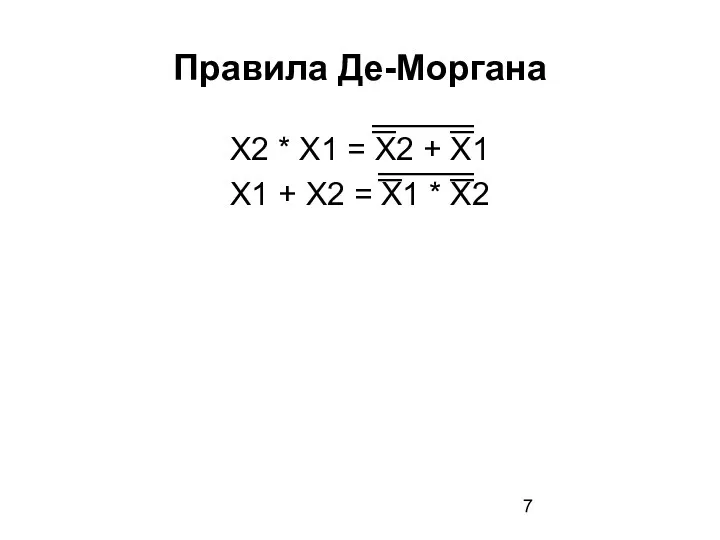

- 7. Правила Де-Моргана X2 * X1 = X2 + X1 X1 + X2 = X1 * X2

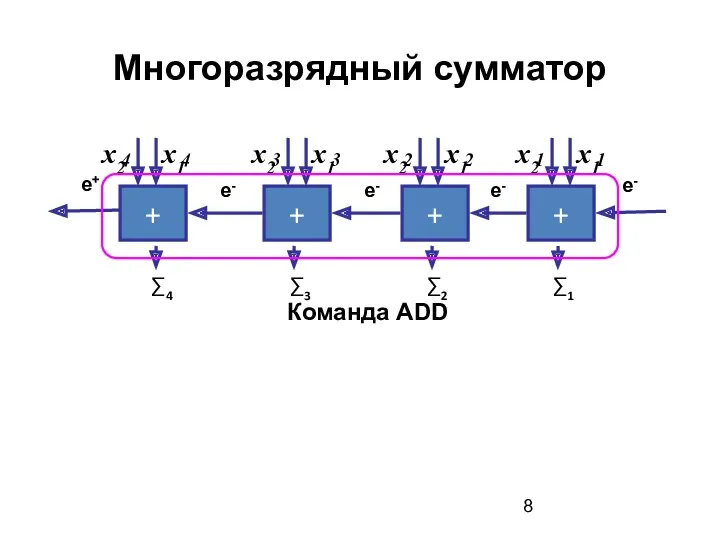

- 8. Многоразрядный сумматор + + + + ∑1 ∑2 ∑3 ∑4 e- e- e- e- e+ Команда

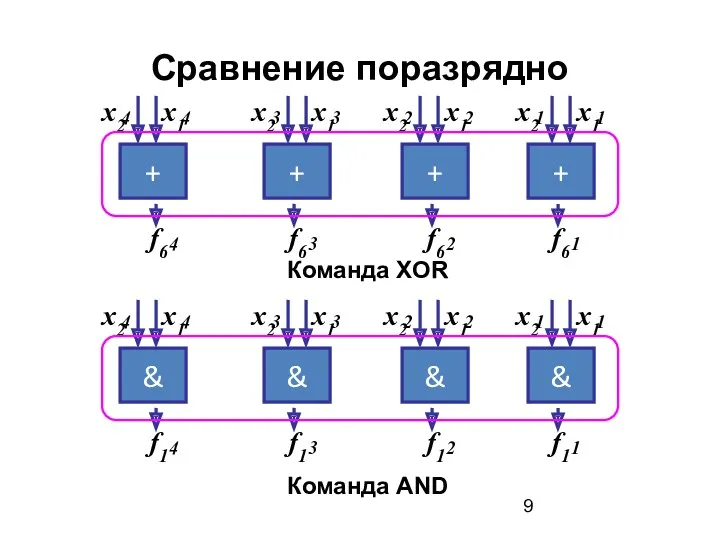

- 9. Сравнение поразрядно + + + + Команда XOR & & & & Команда AND

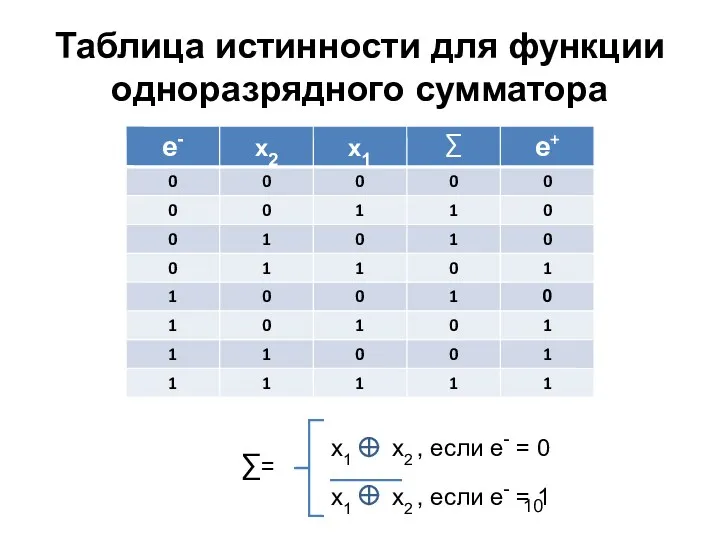

- 10. ∑= x1 x2 , если е- = 0 x1 x2 , если е- = 1 Таблица

- 11. Функциональная схема полного одноразрядного сумматора

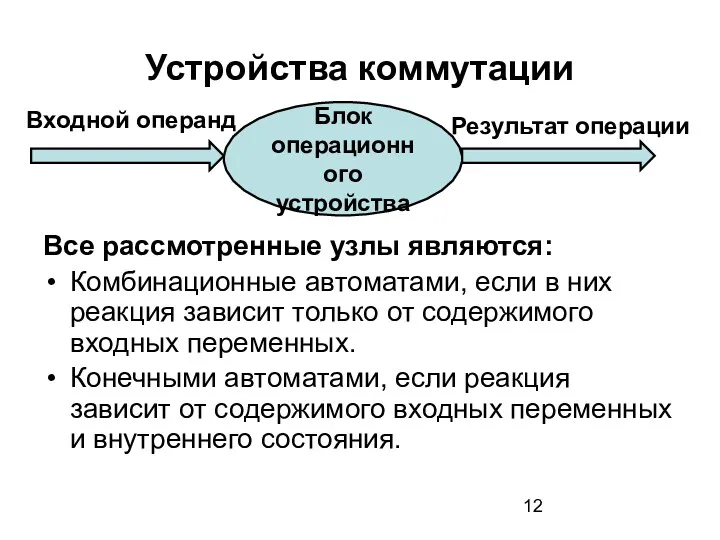

- 12. Устройства коммутации Все рассмотренные узлы являются: Комбинационные автоматами, если в них реакция зависит только от содержимого

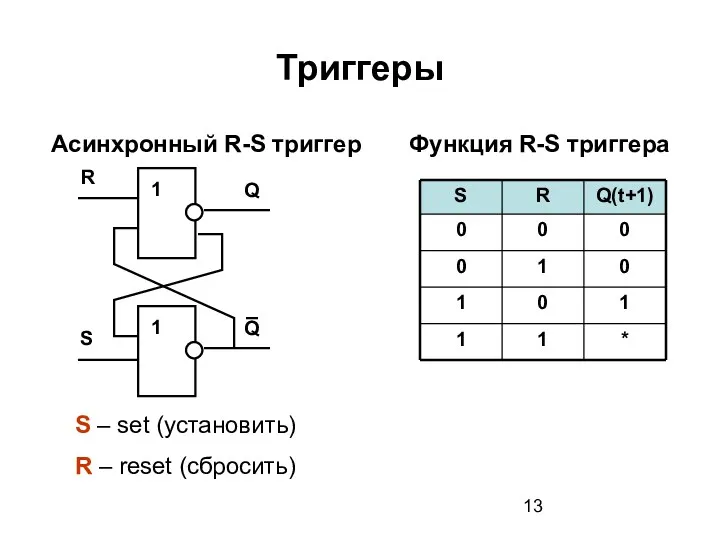

- 13. Триггеры Асинхронный R-S триггер S – set (установить) R – reset (сбросить) Функция R-S триггера

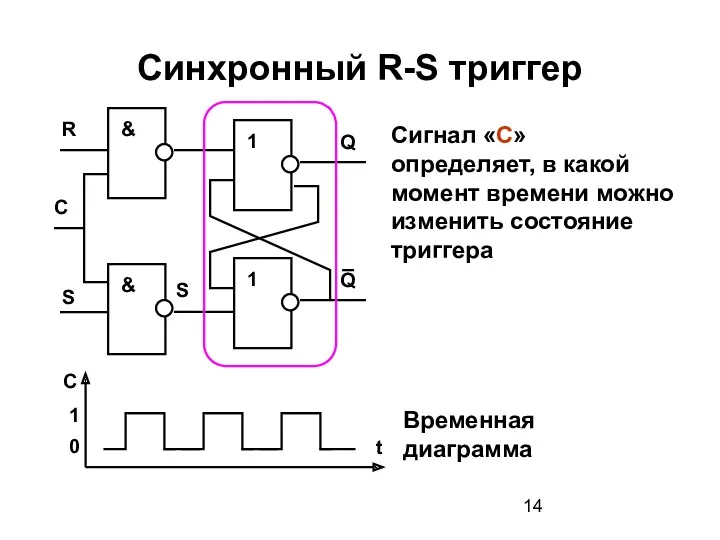

- 14. Синхронный R-S триггер Сигнал «С» определяет, в какой момент времени можно изменить состояние триггера Временная диаграмма

- 16. Скачать презентацию

Заповедники Красноярского края

Заповедники Красноярского края Если друг оказался вдруг (3). Крах банка Берингс

Если друг оказался вдруг (3). Крах банка Берингс тема обозначения числа 11

тема обозначения числа 11 Влияние управленческих воздействий на рост маржинальности аптеки №7 ООО Бережная Аптека

Влияние управленческих воздействий на рост маржинальности аптеки №7 ООО Бережная Аптека Нахождение дроби от числа и числа по его дроби

Нахождение дроби от числа и числа по его дроби презентация к уроку географии Облака и их виды

презентация к уроку географии Облака и их виды Педагогическая теория Константина Дмитриевича Ушинского (1824—1870)

Педагогическая теория Константина Дмитриевича Ушинского (1824—1870) Устойчивость автоматических систем регулирования

Устойчивость автоматических систем регулирования Металлические конструкции, включая сварку. Элементы и соединения

Металлические конструкции, включая сварку. Элементы и соединения Осадочные горные породы

Осадочные горные породы Конструирование механически обрабатываемых деталей

Конструирование механически обрабатываемых деталей Результаты выращивания форели в условиях КФХ Горное

Результаты выращивания форели в условиях КФХ Горное 어린이1반. 봄봄 왔어요^^

어린이1반. 봄봄 왔어요^^ Решето Эратосфена

Решето Эратосфена Развитие автопромышленности. История моей профессии

Развитие автопромышленности. История моей профессии Арматура трубопроводов

Арматура трубопроводов Study the examples in groups and say when the Present Continuous is used

Study the examples in groups and say when the Present Continuous is used Заводы Харькова

Заводы Харькова Tromboflebit. Obiectivele principale în farmacoterapia tromboflebitelor

Tromboflebit. Obiectivele principale în farmacoterapia tromboflebitelor Психолого – педагогические проблемы у дошкольников. Агрессия

Психолого – педагогические проблемы у дошкольников. Агрессия Синустық брадикардия

Синустық брадикардия Мастер-класс Пасхальный подарок

Мастер-класс Пасхальный подарок Частотные методы анализа показателей качества

Частотные методы анализа показателей качества The east region of Kazakhstan

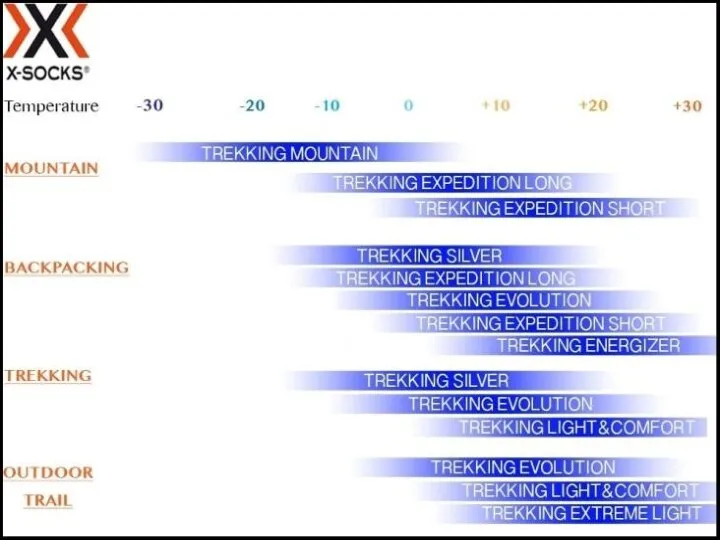

The east region of Kazakhstan X-Socks Trekking

X-Socks Trekking Молодежный клуб Jugend Blumenfeld

Молодежный клуб Jugend Blumenfeld Бытовые электрические приборы

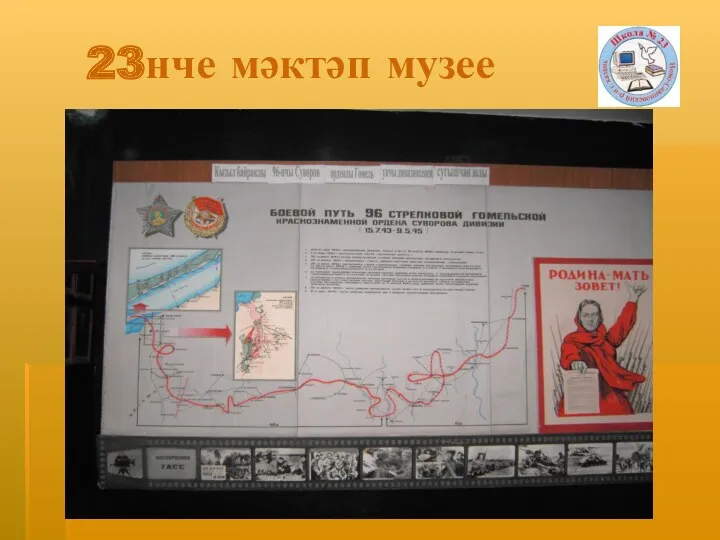

Бытовые электрические приборы Сугышчан дан мәктәп музее

Сугышчан дан мәктәп музее