Содержание

- 2. Базовые логические элементы Компьютер выполняет арифметические и логические операции при помощи т.н. базовых логических элементов, которые

- 3. Составные элементы Любая логическая операция может быть представлена через конъюнкцию, дизъюнкцию и инверсию Любой сколь угодно

- 4. Сигналы-аргументы и сигналы-функции Вентили оперируют с электрическими импульсами: Импульс имеется – логический смысл сигнала «1» Импульса

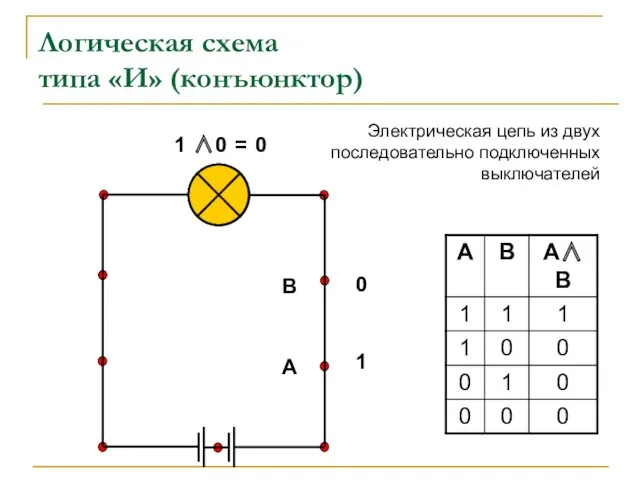

- 5. Логическая схема типа «И» (конъюнктор) 1 ∧ 0 = 0 1 0 A В Электрическая цепь

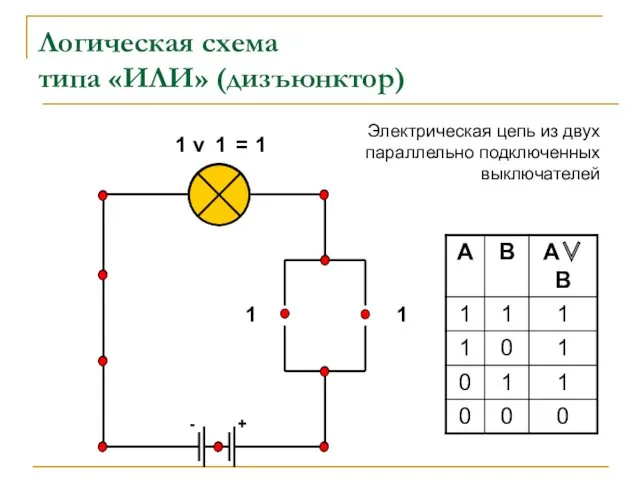

- 6. + - Логическая схема типа «ИЛИ» (дизъюнктор) 1 1 1 v 1 = 1 Электрическая цепь

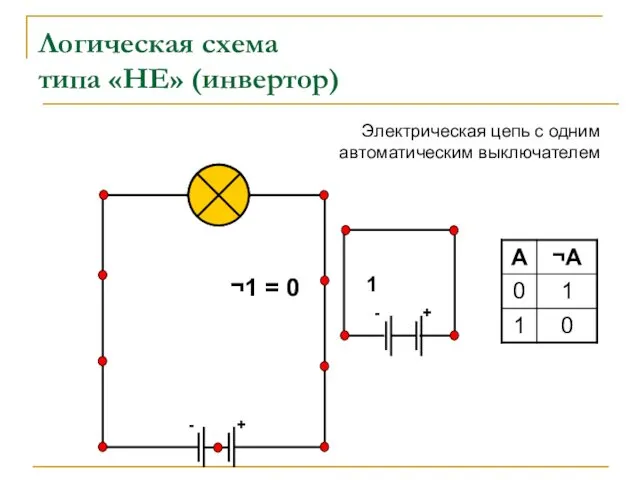

- 7. + - Логическая схема типа «НЕ» (инвертор) + - ¬1 = 0 1 Электрическая цепь с

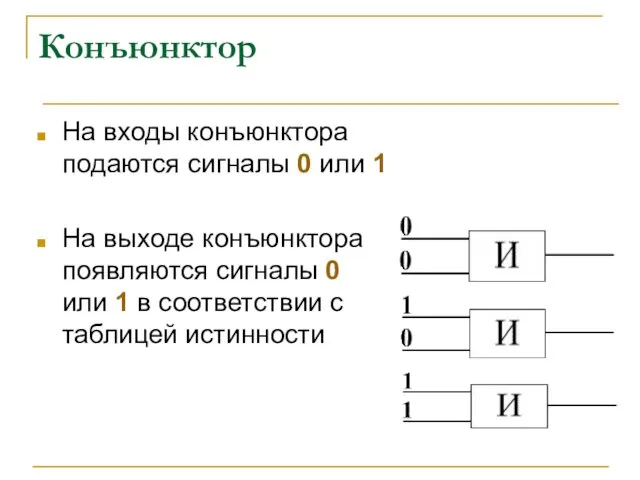

- 8. Конъюнктор На входы конъюнктора подаются сигналы 0 или 1 На выходе конъюнктора появляются сигналы 0 или

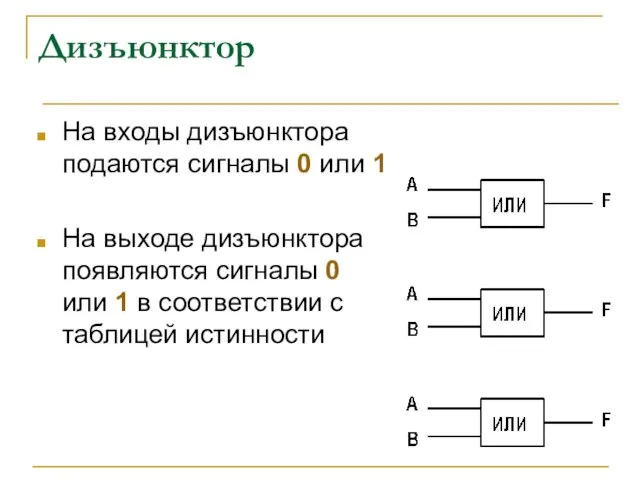

- 9. Дизъюнктор На входы дизъюнктора подаются сигналы 0 или 1 На выходе дизъюнктора появляются сигналы 0 или

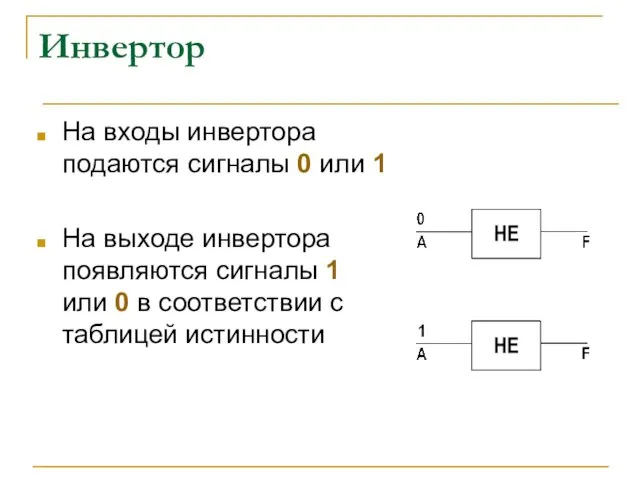

- 10. Инвеpтор На входы инвертора подаются сигналы 0 или 1 На выходе инвертора появляются сигналы 1 или

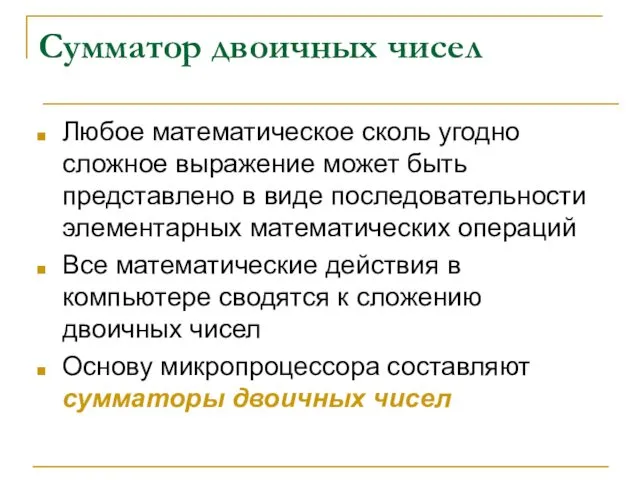

- 11. Сумматор двоичных чисел Любое математическое сколь угодно сложное выражение может быть представлено в виде последовательности элементарных

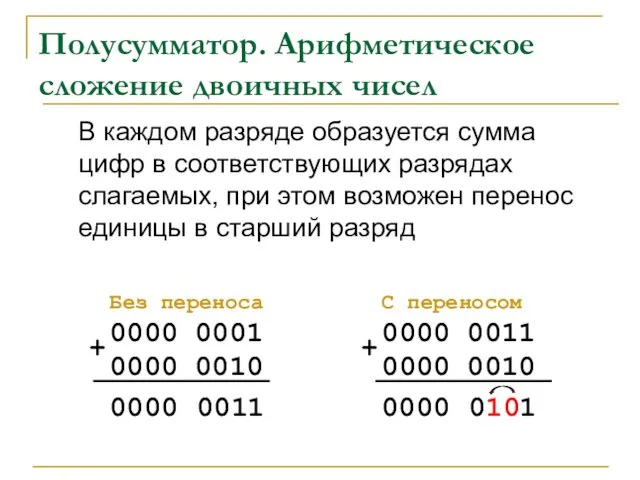

- 12. Полусумматор. Арифметическое сложение двоичных чисел В каждом разряде образуется сумма цифр в соответствующих разрядах слагаемых, при

- 13. Обозначим слагаемые через А и В, перенос – через Р, а сумму – через S Таблица

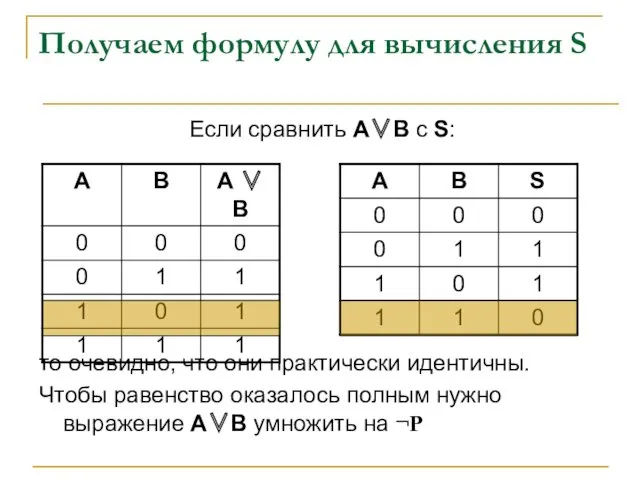

- 14. Получаем формулу для вычисления S Если сравнить А∨В c S: то очевидно, что они практически идентичны.

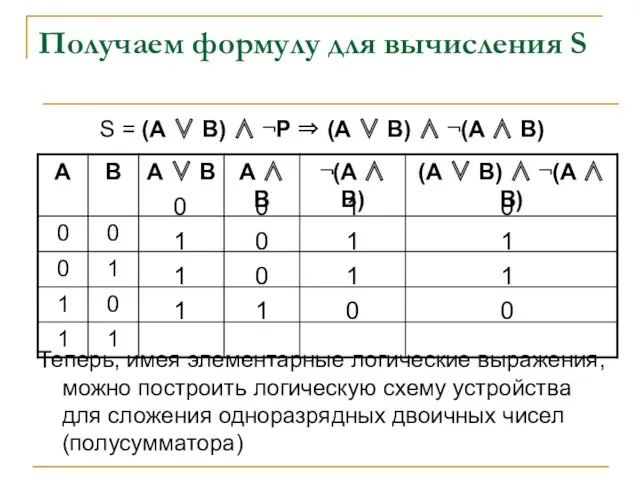

- 15. Получаем формулу для вычисления S S = (А ∨ В) ∧ ¬P ⇒ (А ∨ В)

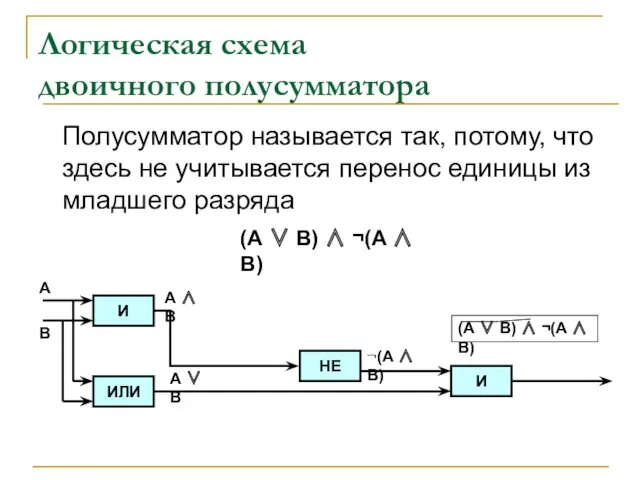

- 16. Логическая схема двоичного полусумматора Полусумматор называется так, потому, что здесь не учитывается перенос единицы из младшего

- 17. Полный одноразрядный сумматор Должен иметь три входа (А, В и Р0) и два выхода (S и

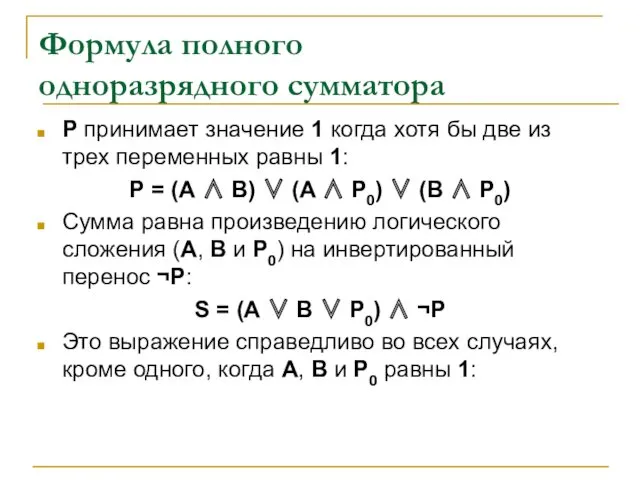

- 18. Формула полного одноразрядного сумматора Р принимает значение 1 когда хотя бы две из трех переменных равны

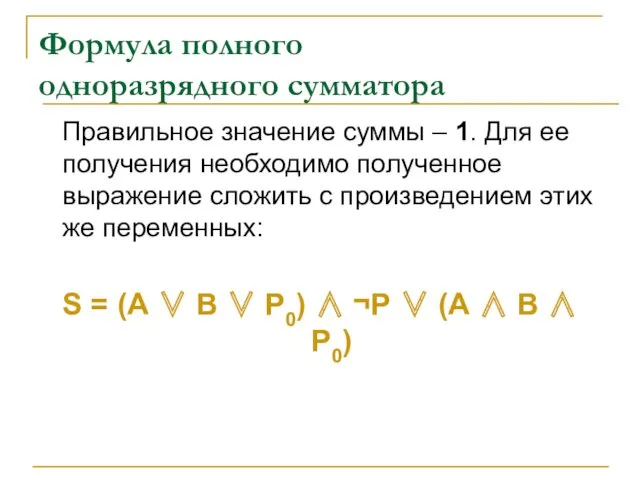

- 19. Формула полного одноразрядного сумматора Правильное значение суммы – 1. Для ее получения необходимо полученное выражение сложить

- 20. Многоразрядный сумматор Построен на основе полных одноразрядных сумматоров (по одному на каждый разряд), причем таким образом,

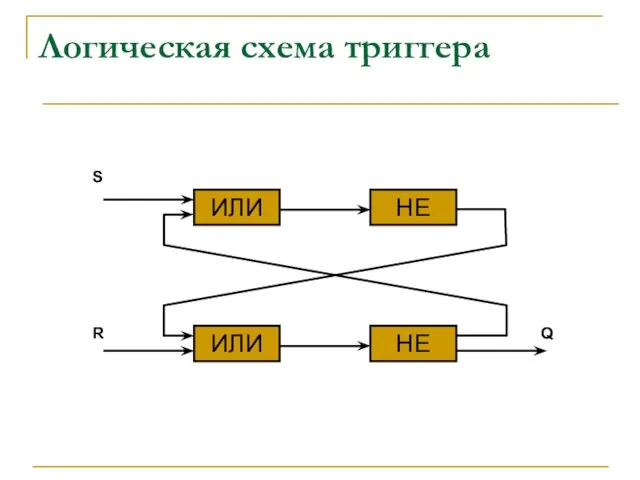

- 21. Триггер Важнейшая структурная единица оперативной памяти и регистров процессора Состоит из двух логических элементов «ИЛИ» и

- 22. Логическая схема триггера ИЛИ ИЛИ НЕ НЕ S R Q

- 24. Скачать презентацию

Презентазия Посадка лука

Презентазия Посадка лука Теплоснабжение промышленных предприятий

Теплоснабжение промышленных предприятий Обновлённый ФПУ: проблемы и пути решения

Обновлённый ФПУ: проблемы и пути решения Расчет объемов стока с промышленной площадки предприятия и определение предельного допустимого стока

Расчет объемов стока с промышленной площадки предприятия и определение предельного допустимого стока UNESCO

UNESCO Классификация и структуры моделей

Классификация и структуры моделей Мой портфолио Диск

Мой портфолио Диск Действия над рациональными числами

Действия над рациональными числами Влияние эмульсии на работу УЭЦН

Влияние эмульсии на работу УЭЦН Морфемика и орфография. Повторение

Морфемика и орфография. Повторение Дидактические игры по сенсорному воспитанию для детей раннего возраста.

Дидактические игры по сенсорному воспитанию для детей раннего возраста. PR in non-profit organizations

PR in non-profit organizations Презентация к уроку Средства музыкальной выразительности

Презентация к уроку Средства музыкальной выразительности Islamic مبادرة life makers

Islamic مبادرة life makers Программа авиапутешествия Москва – Кейптаун

Программа авиапутешествия Москва – Кейптаун Собаки - герои Презентация.

Собаки - герои Презентация. Доноведение 4 класс Мой крайпрезентация

Доноведение 4 класс Мой крайпрезентация Вариация и рондо

Вариация и рондо Андрей Платонович Платонов. Виртуальная выставка, к 120 – летию со дня рождения советского писателя

Андрей Платонович Платонов. Виртуальная выставка, к 120 – летию со дня рождения советского писателя Фрактал. Три основные вида фракталов

Фрактал. Три основные вида фракталов Сегментні регістри. (Лекція 1.2)

Сегментні регістри. (Лекція 1.2) Проектирование средней школы на 12 классов в городе Ревда

Проектирование средней школы на 12 классов в городе Ревда Нормальная физиология

Нормальная физиология Новая ситуация в Восточной Европе

Новая ситуация в Восточной Европе Штамповые испытания нежестких дорожных конструкций

Штамповые испытания нежестких дорожных конструкций Автоматизация звукопроизношения

Автоматизация звукопроизношения Ғылыми экспериментті жүргізу тәртібі және экспериментаторға қойылатын талаптар туралы

Ғылыми экспериментті жүргізу тәртібі және экспериментаторға қойылатын талаптар туралы Организация проектной и исследовательской деятельности обучающихся в объединениях в системе дополнительного образования

Организация проектной и исследовательской деятельности обучающихся в объединениях в системе дополнительного образования