Содержание

- 2. 4096tb@gmail.com Тема письма: БГУИР. … . Ковалевский Вячеслав Викторович

- 3. Лекция 1. Представление информации. Системы счисления. Формат с фиксированной запятой План лекции: История развития вычислительной техники.

- 4. Лекция 2. Формат с плавающей запятой. Стандарт IEEE 754. Погрешности. Обратная польская запись План лекции: Формат

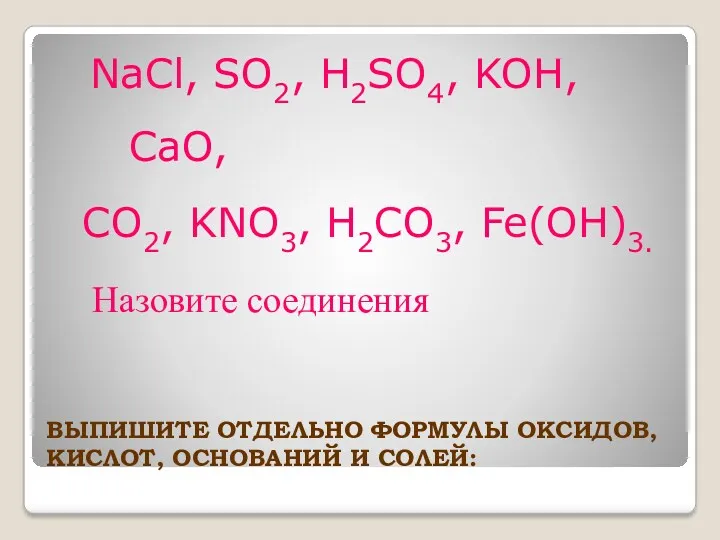

- 5. Лекция 3. Логические основы ЭВМ. Минимизация. План лекции: Понятия алгебры логики. Аксиомы и законы алгебры логики.

- 6. Лекция 4. Основы схемотехники ЭВМ. План лекции: Логический элемент как физическое устройство. RS-триггер – бистабильная ячейка.

- 7. Логический элемент как физическое устройство Для описания функционирования цифровых схем используется алгебра логики (Булева алгебра). В

- 8. Логические (комбинационные) схемы Логическая схема (ЛС), или схема «без памяти», состоит из логических элементов (ЛЭ), соединенных

- 9. Логические элементы ИЛИ И НЕ И-НЕ Логической функцией является функция: у = f(x1, x2,… xn), принимающая

- 10. Логические элементы ИЛИ И НЕ И-НЕ ИЛИ-НЕ Исключающее ИЛИ Логической функцией является функция: у = f(x1,

- 11. Пример реализации ЛФ («Сумматор» -суммирование чисел (2)) «Сумматор» является неотъемлемой частью АЛУ любого процессора. Составной частью

- 12. Пример реализации ЛФ (Схема охранной сигнализации на ЛЭ) Генератор (Г) вырабатывает сигнал сирены, подавая его на

- 13. Триггер Триггеры (англ. Trigger - защёлка, спусковой крючок), являются простейшими устройствами с памятью. Если выходные сигналы

- 14. Схема с обратной связью Обратная связь

- 15. Схема с обратной связью 1 1 1 1 ? ? ? ? ? ? Обратная связь

- 16. Схема с обратной связью 1 1 1 1 1 1 0 1 0 1 0 1

- 17. Схема с обратной связью 1 1 0 1 1 1 1 0 1 1 0 1

- 18. Схема с обратной связью 0 0 1 1 0 1 1 0 0 1 1 0

- 19. RS-триггер RS-триггер - это триггер с раздельной установкой состояний логического нуля и единицы (с раздельным запуском).

- 20. RS-триггер – бистабильная ячейка Таблица переходов

- 21. RS-триггер – бистабильная ячейка Пример временной диаграммы

- 22. RS-триггер – бистабильная ячейка Пример временной диаграммы

- 23. RS-триггер – бистабильная ячейка Таблица переходов

- 24. RS-триггер – бистабильная ячейка Таблица переходов С

- 25. RS-триггер – бистабильная ячейка Пример реализации на РЭ компонентах

- 26. JK-триггер – бистабильная ячейка Таблица переходов Исключено запрещённое состояние - при подаче двух единиц JK триггер

- 27. D-триггер (англ. Delay-задержка) Таблица переходов В RS триггере сигналы установки и сброса не могут появляться одновременно,

- 28. D-триггер Пример временной диаграммы

- 29. T-триггер (счетный) Таблица переходов После поступления на вход T импульса, состояние триггера меняется на прямо противоположное

- 30. T-триггер Пример временной диаграммы

- 31. Функциональные узлы ЭВМ Регистры Счетчики Шифраторы Дешифраторы Мультиплексоры Сумматоры АЛУ

- 32. Регистры Регистр — устройство, используемое для хранения n-разрядных двоичных данных и выполнения преобразований над ними. Регистр

- 33. Регистры …

- 34. Счетчики C 0 1 2 3 На выходах двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики

- 35. Дешифраторы D2 D1 D0 0 1 1 y0 y1 y2 y3 – active y4 y5 y6

- 36. Шифраторы m вых n вх Шифратор (англ. encoder) - логическое устройство, выполняющее логическую функцию преобразования позиционного

- 37. Мультиплексоры S=0 ⇒ Y = A S=1 ⇒ Y = B Устройство, имеющее несколько сигнальных входов,

- 38. Сумматоры Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов,

- 39. Сумматоры Комбинационный сумматор An-1 … A0 Bn-1 … B0 Sn-1 … S0 S = A +

- 40. Сумматоры Накапливающий сумматор S = S + B + C0 Сумматор накапливающего типа - это схема

- 41. Арифметико-логическое устройство (АЛУ) В АЛУ выполняются арифметические и логические операции над двоичными числами. Состоит из сумматоров,

- 42. АЛУ (ALU) Комбинационное АЛУ An-1 … A0 Bn-1 … B0 Yn-1 … Y0 Y = F(A,

- 43. АЛУ (ALU) АЛУ накапливающего типа

- 44. Структура процессора

- 45. Регистры процессора

- 46. Регистр признаков (PSW) Cлово состояния процессора (ССП) англ. PSW — Processor Status Word

- 47. Структура процессора Intel

- 48. Структура компьютера

- 49. Структура компьютера

- 51. Скачать презентацию

Аппликация из кругов

Аппликация из кругов Транспортирование строительных грузов

Транспортирование строительных грузов ПРЕЗЕНТАЦИЯ ОБРАЗОВАТЕЛЬНОЙ ПРОГРАММЫ

ПРЕЗЕНТАЦИЯ ОБРАЗОВАТЕЛЬНОЙ ПРОГРАММЫ The fundamentals of english grammar. The verb to be

The fundamentals of english grammar. The verb to be Обыкновенные дроби

Обыкновенные дроби 8 класс Чистые вещества и смеси

8 класс Чистые вещества и смеси Личное дело воспитанника

Личное дело воспитанника Основы логики. Логические операции и таблицы истинности

Основы логики. Логические операции и таблицы истинности Урок: Окислительно-восстановительные реакции 11 класс

Урок: Окислительно-восстановительные реакции 11 класс Аппараты до 1000В. Рубильники

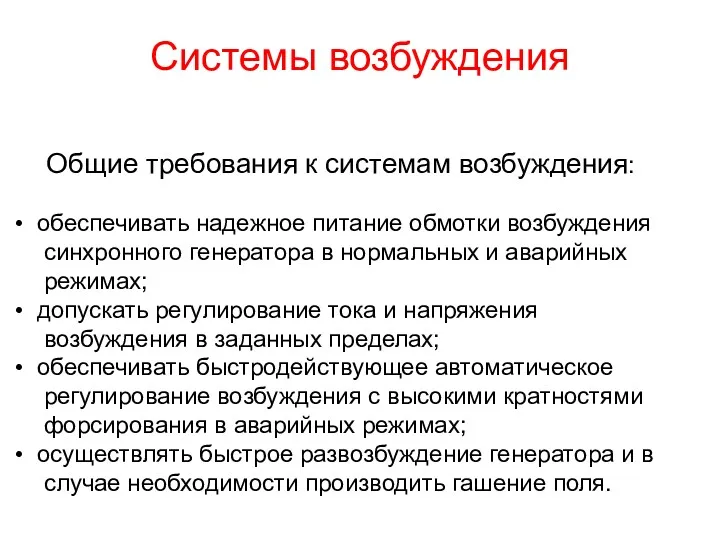

Аппараты до 1000В. Рубильники Системы возбуждения

Системы возбуждения Проблемы формирования нравственных ценностей у детей дошкольного возраста.

Проблемы формирования нравственных ценностей у детей дошкольного возраста. Digital Design and Computer Architecture. Introdution

Digital Design and Computer Architecture. Introdution Механизм государства: понятие и структура

Механизм государства: понятие и структура Реле в электротехнике

Реле в электротехнике Классный час Берегите Язык

Классный час Берегите Язык A FPGA Accelerated AI for Connect-5

A FPGA Accelerated AI for Connect-5 Фразеологизмы. Мультимедийный урок

Фразеологизмы. Мультимедийный урок презентация к уроку: Мы изучаем США.

презентация к уроку: Мы изучаем США. Презентация Степень окисления 8 класс

Презентация Степень окисления 8 класс Порядок и формы проведения государственной итоговой аттестации выпускников 9 классов в 2016- 2017 учебном году

Порядок и формы проведения государственной итоговой аттестации выпускников 9 классов в 2016- 2017 учебном году Сказка Звездочки

Сказка Звездочки Поверхносная закалка стали

Поверхносная закалка стали Что такое право

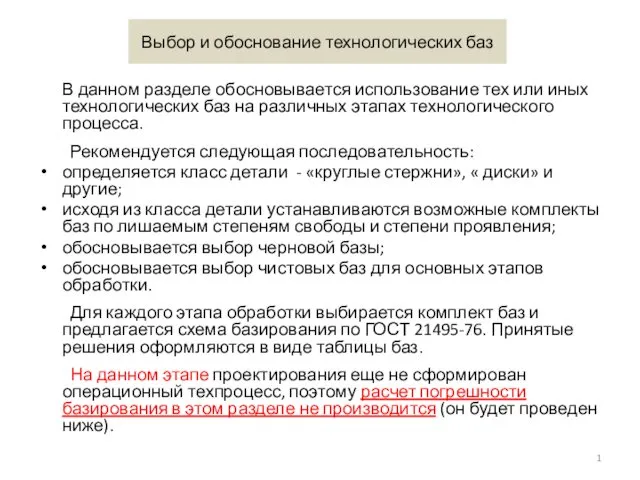

Что такое право Выбор и обоснование технологических баз

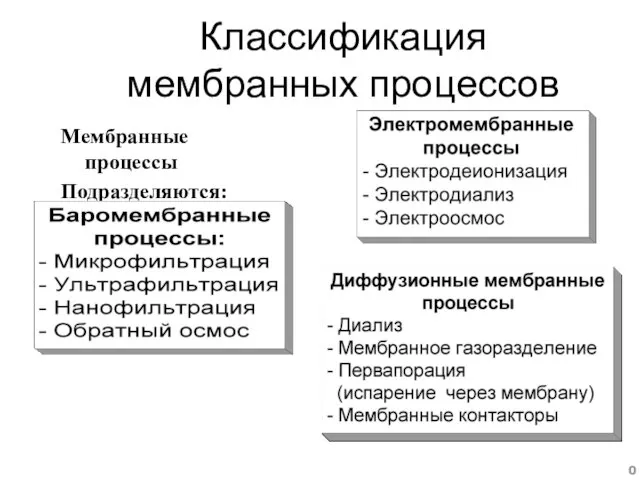

Выбор и обоснование технологических баз Классификация мембранных процессов

Классификация мембранных процессов ПОЛЯРИЗАЦИЯ

ПОЛЯРИЗАЦИЯ Асинхронный тяговый привод

Асинхронный тяговый привод