Содержание

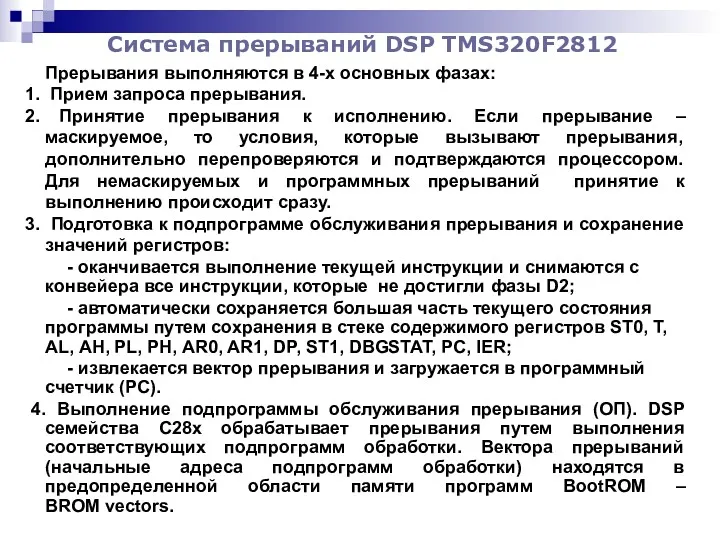

- 2. Система прерываний DSP TMS320F2812 Прерывания выполняются в 4-х основных фазах: Прием запроса прерывания. Принятие прерывания к

- 3. Система прерываний DSP TMS320F2812

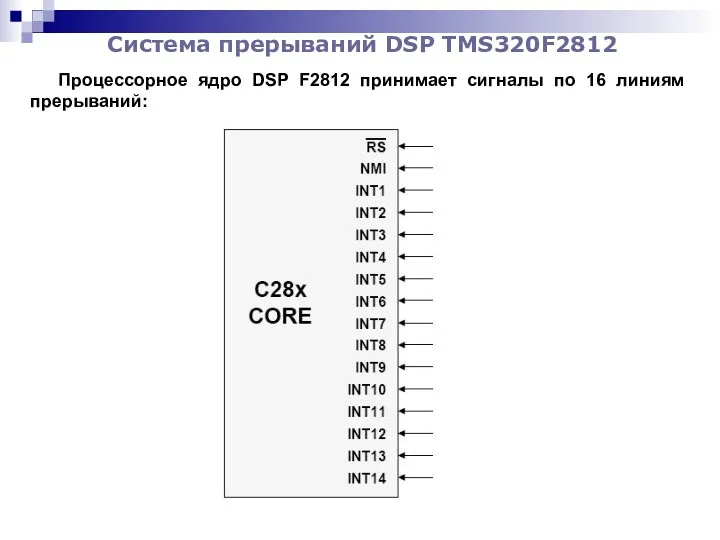

- 4. Система прерываний DSP TMS320F2812 Процессорное ядро DSP F2812 принимает сигналы по 16 линиям прерываний:

- 5. Система прерываний DSP TMS320F2812 Источники прерываний в DSP F2812:

- 6. 32-битные таймеры ядра ЦСП TMS320F28x Сигналы прерываний, формируемые CPU-таймерами, связаны с прерываниями ядра следующим образом:

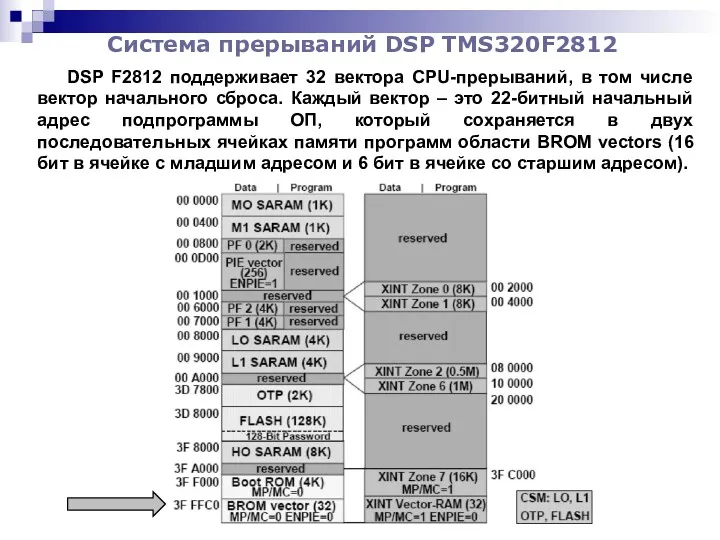

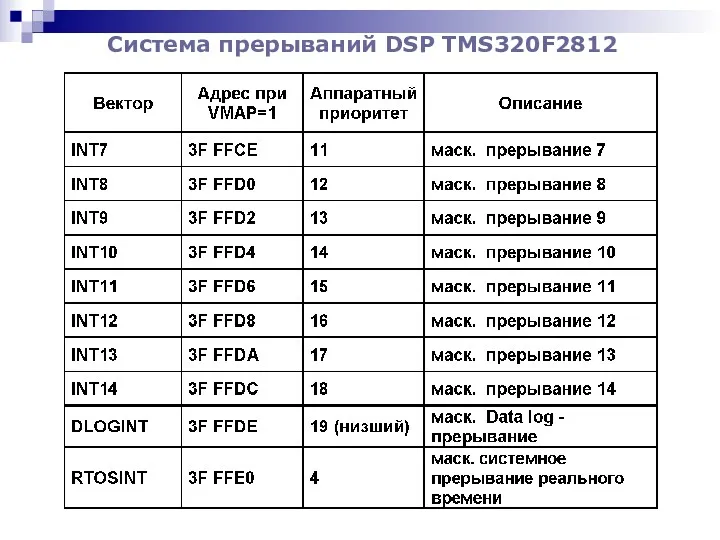

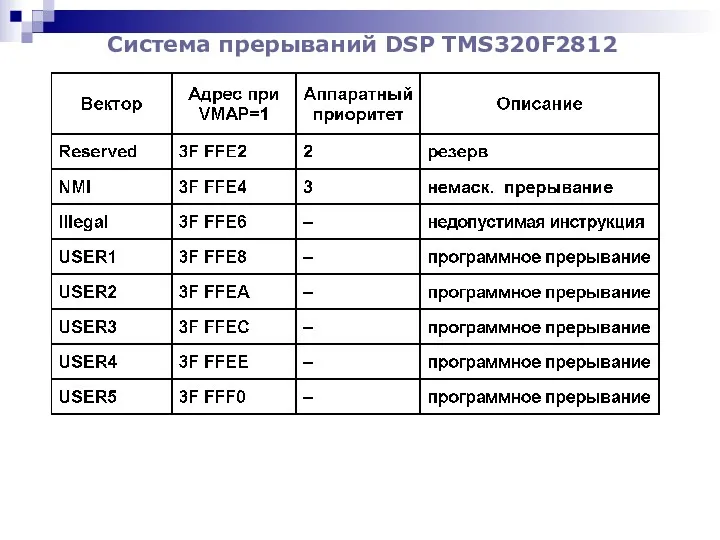

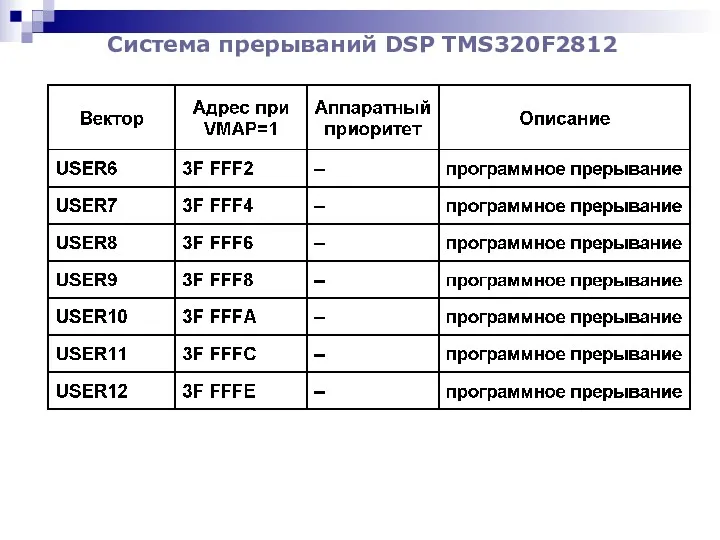

- 7. Система прерываний DSP TMS320F2812 DSP F2812 поддерживает 32 вектора CPU-прерываний, в том числе вектор начального сброса.

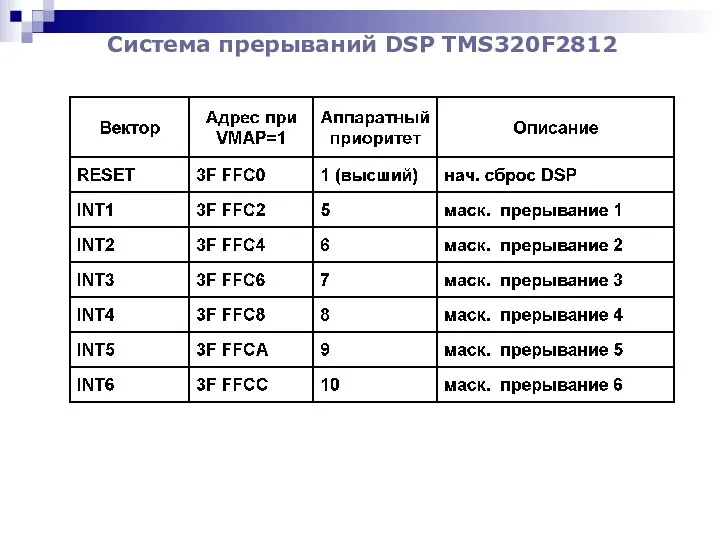

- 8. Система прерываний DSP TMS320F2812

- 9. Система прерываний DSP TMS320F2812

- 10. Система прерываний DSP TMS320F2812

- 11. Система прерываний DSP TMS320F2812

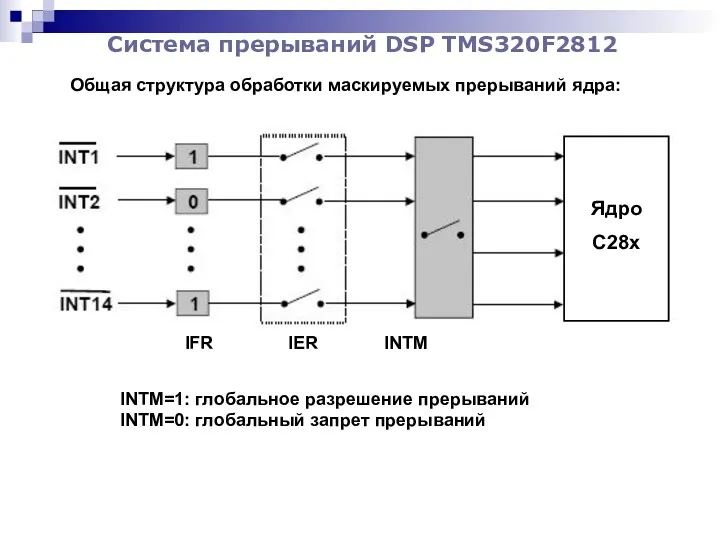

- 12. Система прерываний DSP TMS320F2812 Общая структура обработки маскируемых прерываний ядра: IFR IER INTM Ядро C28x INTM=1:

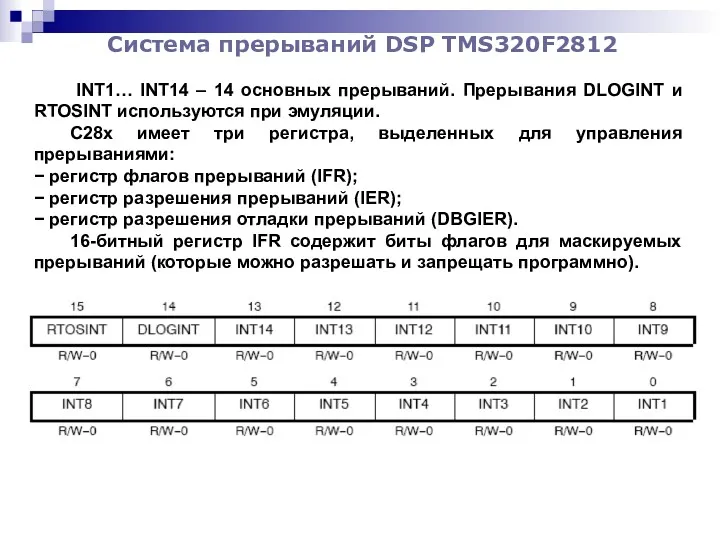

- 13. Система прерываний DSP TMS320F2812 INT1… INT14 – 14 основных прерываний. Прерывания DLOGINT и RTOSINT используются при

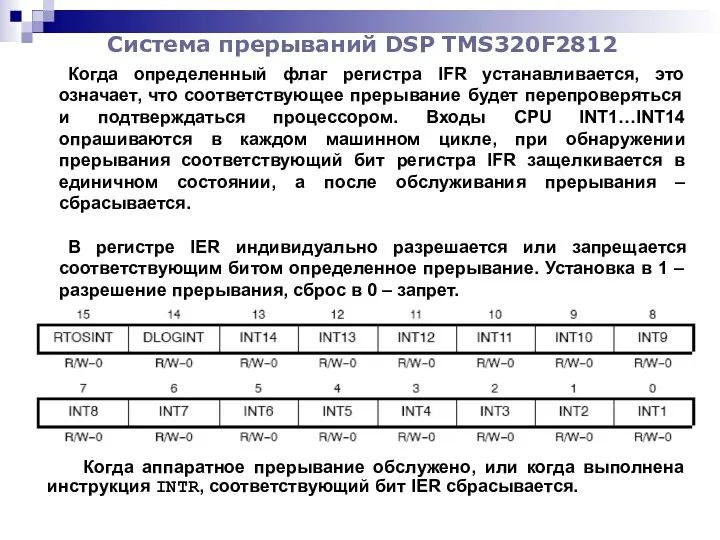

- 14. Система прерываний DSP TMS320F2812 Когда определенный флаг регистра IFR устанавливается, это означает, что соответствующее прерывание будет

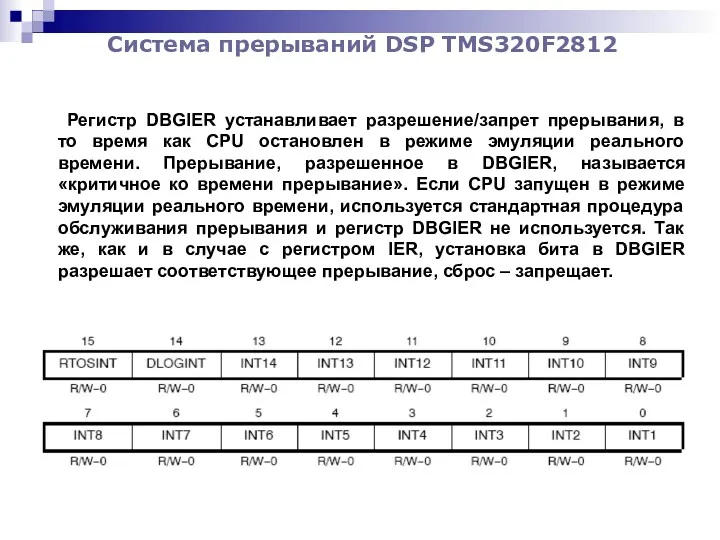

- 15. Система прерываний DSP TMS320F2812 Регистр DBGIER устанавливает разрешение/запрет прерывания, в то время как CPU остановлен в

- 16. Система прерываний DSP TMS320F2812 Стандартная процедура выполнения маскируемого прерывания:

- 17. Система прерываний DSP TMS320F2812 В случае использования PIE-контроллера, таблица адресов векторов прерываний расширяется. PIE-контроллер может поддерживать

- 18. Система прерываний DSP TMS320F2812 Таблица источников прерываний в PIE-контроллере: Приоритет

- 19. Система прерываний DSP TMS320F2812 Каждая группа (строка из 8 элементов) мультиплексируется в одно из прерываний ядра

- 20. Система прерываний DSP TMS320F2812 Каждое из 96 прерываний поддерживается единственным вектором прерывания, размещенном в специально предназначенной

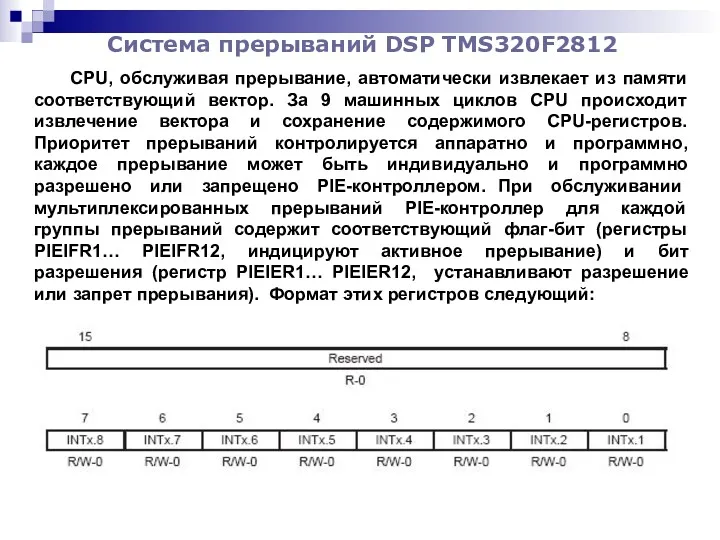

- 21. Система прерываний DSP TMS320F2812 CPU, обслуживая прерывание, автоматически извлекает из памяти соответствующий вектор. За 9 машинных

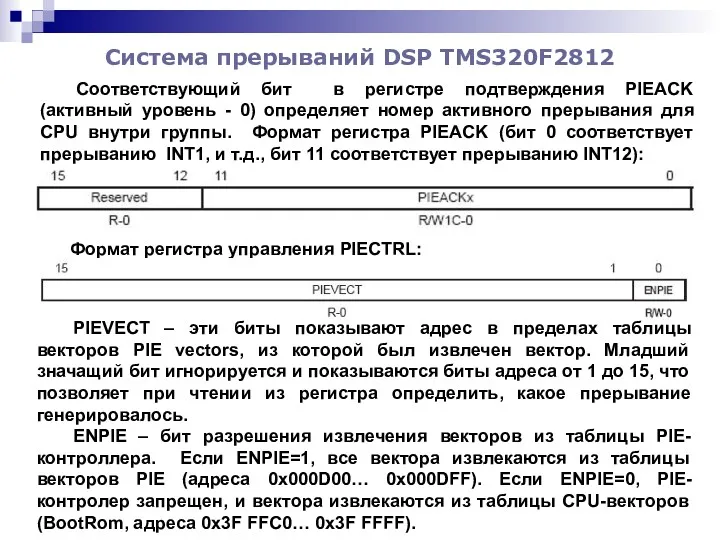

- 22. Система прерываний DSP TMS320F2812 Соответствующий бит в регистре подтверждения PIEACK (активный уровень - 0) определяет номер

- 23. Система прерываний DSP TMS320F2812

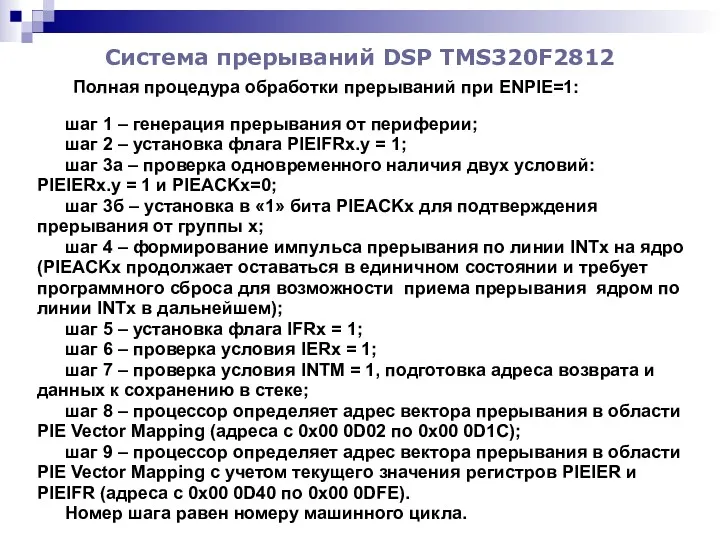

- 24. Система прерываний DSP TMS320F2812 Полная процедура обработки прерываний при ENPIE=1: шаг 1 – генерация прерывания от

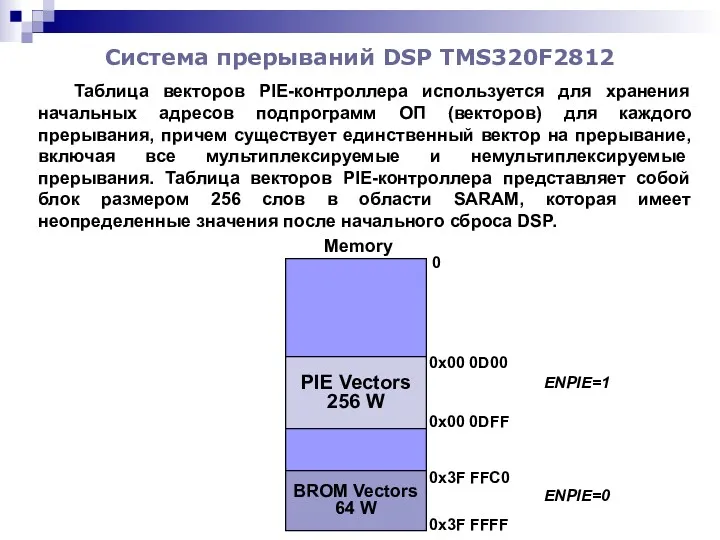

- 25. Система прерываний DSP TMS320F2812 Таблица векторов PIE-контроллера используется для хранения начальных адресов подпрограмм ОП (векторов) для

- 27. Скачать презентацию

Средства технической диагностики вагонов в эксплуатации

Средства технической диагностики вагонов в эксплуатации Главные параметры карьера

Главные параметры карьера Отопление зданий

Отопление зданий Обувные товары

Обувные товары работа с одаренными детьми

работа с одаренными детьми Жизнь и деятельность Менделеева Д.И.

Жизнь и деятельность Менделеева Д.И. Презентция проекта ТЮМЕНЬ - МОЙ ГОРОД РОДНОЙ!

Презентция проекта ТЮМЕНЬ - МОЙ ГОРОД РОДНОЙ! Преемственность дошкольного и школьного образования с учетом федеральных государственных требований

Преемственность дошкольного и школьного образования с учетом федеральных государственных требований Тепло сердец для наших любимых мам

Тепло сердец для наших любимых мам Комитет по строительству, архитектуре и развитию города Барнаула

Комитет по строительству, архитектуре и развитию города Барнаула Презентация без названия

Презентация без названия 3ds max 15. Эскиз обретает объем. (Часть 2)

3ds max 15. Эскиз обретает объем. (Часть 2) Плюсы занятий арттерапии

Плюсы занятий арттерапии Глобальні проблеми людства

Глобальні проблеми людства Близнецы - чудо жизни

Близнецы - чудо жизни Совместное общество (общество участия)

Совместное общество (общество участия) Economics as a science

Economics as a science Погода, климат.

Погода, климат. Виды конденсаторов

Виды конденсаторов Образование централизованных государств в Западной Европе (XI – XV века)

Образование централизованных государств в Западной Европе (XI – XV века) Предмет педагогической науки и ее основные категории

Предмет педагогической науки и ее основные категории презентация Толерантность в решении конфликтов

презентация Толерантность в решении конфликтов Социальный проект Я хочу быть здоровым

Социальный проект Я хочу быть здоровым Приёмы систематизации знаний в географии

Приёмы систематизации знаний в географии Древний Египет. Мифы. Архитектура

Древний Египет. Мифы. Архитектура Презентация к родительскому собранию в ДОУ. Эмоциональное развитие дошкольников.

Презентация к родительскому собранию в ДОУ. Эмоциональное развитие дошкольников. Вечный двигатель

Вечный двигатель Движение небесных тел под действием сил тяготения

Движение небесных тел под действием сил тяготения