Содержание

- 2. Архитектура микропроцессоров Основные характеристики процессора Разрядность количество (двоичных) разрядов в представлении обрабатываемых данных (например, 32) Адресное

- 3. Архитектура микропроцессоров Основные характеристики процессора Система команд процессора полный набор команд, которые может выполнять процессор Регистры

- 4. Архитектура микропроцессоров Большинство выпускаемых в настоящее время процессоров для персональных компьютеров соответствуют архитектуре, впервые реализованной в

- 5. Программная модель микропроцессора IA-32 Регистры высокоскоростные ячейки памяти, расположенные внутри процессора. Доступ к регистрам осуществляется гораздо

- 6. Программная модель микропроцессора IA-32 Регистры общего назначения EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP Предназначены

- 7. Программная модель микропроцессора IA-32 Регистр EAX – аккумулятор – обеспечивает наиболее эффективное выполнение большинства арифметических и

- 8. Программная модель микропроцессора IA-32 Регистр EBX – базовый регистр – обеспечивает наиболее эффективное вычисление адреса операнда

- 9. Программная модель микропроцессора IA-32 Регистр ECX – счетчик – используется как счетчик итераций при организации повторений

- 10. Программная модель микропроцессора IA-32 Регистр EDX – регистр данных – используется при организации ввода-вывода; – обязательно

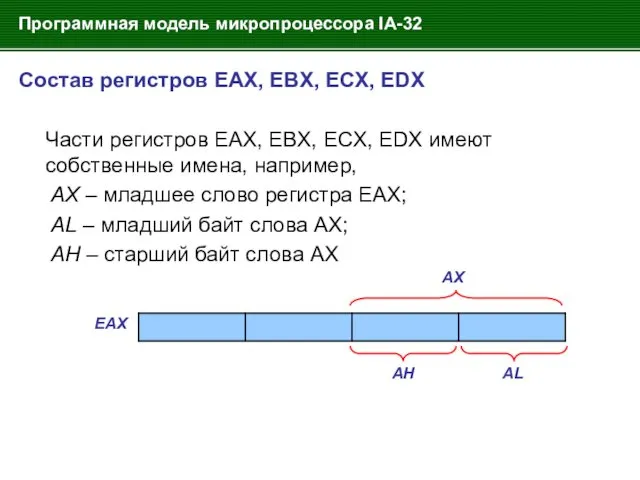

- 11. Программная модель микропроцессора IA-32 Состав регистров EAX, EBX, ECX, EDX Части регистров EAX, EBX, ECX, EDX

- 12. Программная модель микропроцессора IA-32 Регистры ESI, EDI – индексные регистры – используются при выполнении цепочечных (последовательных)

- 13. Программная модель микропроцессора IA-32 Регистры ESP, EBP – указатели стека – используются при обращении к стеку

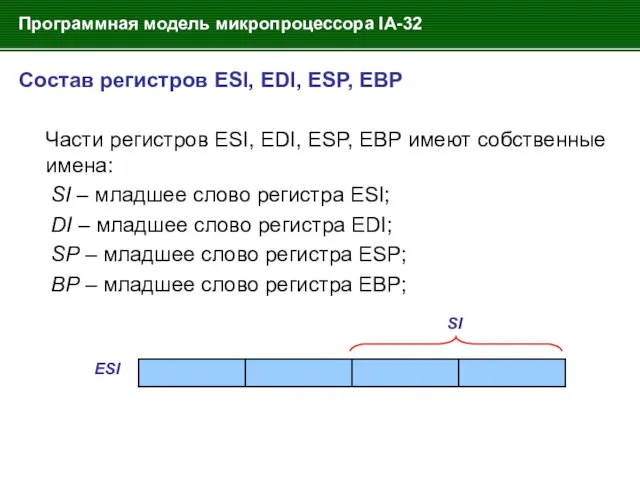

- 14. Программная модель микропроцессора IA-32 Состав регистров ESI, EDI, ESP, EBP Части регистров ESI, EDI, ESP, EBP

- 15. Программная модель микропроцессора IA-32 Сегментные регистры CS, DS, ES, FS, GS, SS Предназначены для организации хранения

- 16. Программная модель микропроцессора IA-32 Регистр EIP – указатель инструкций – содержит адрес (указатель) очередной инструкции, подлежащей

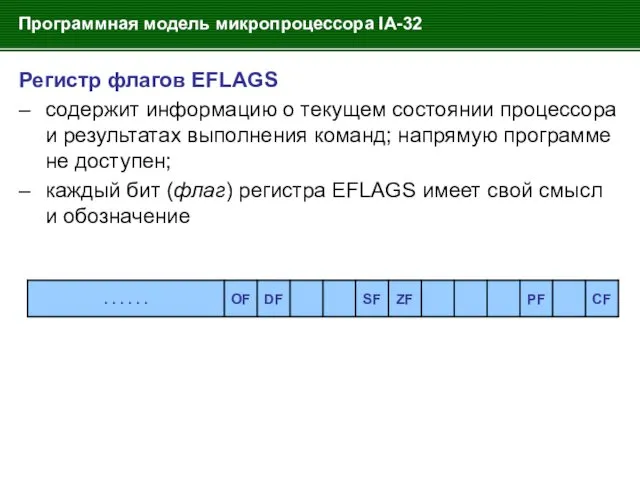

- 17. Программная модель микропроцессора IA-32 Регистр флагов EFLAGS – содержит информацию о текущем состоянии процессора и результатах

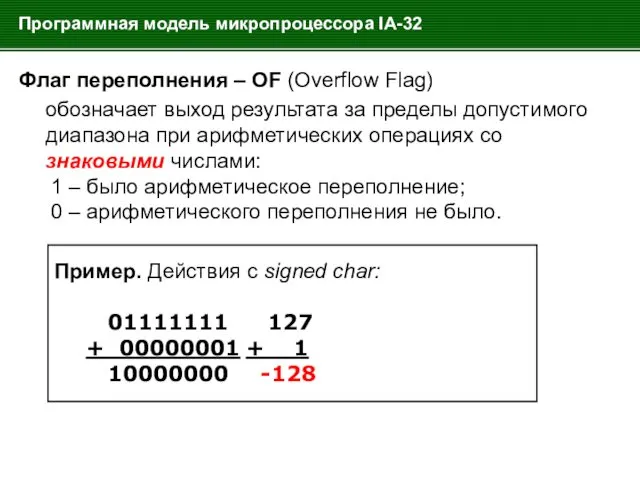

- 18. Программная модель микропроцессора IA-32 Флаг переполнения – OF (Overflow Flag) обозначает выход результата за пределы допустимого

- 19. Программная модель микропроцессора IA-32 Флаг направления – DF (Direction Flag) задает направление изменения индексных регистров ESI,

- 20. Программная модель микропроцессора IA-32 Флаг знака – SF (Sign Flag) показывает знак (старший бит) результата в

- 21. Программная модель микропроцессора IA-32 Флаг нуля – ZF (Zero Flag) показывает, был ли нулевым результат последней

- 22. Программная модель микропроцессора IA-32 Флаг четности – PF (Parity Flag) показывает, сколько единичных бит было в

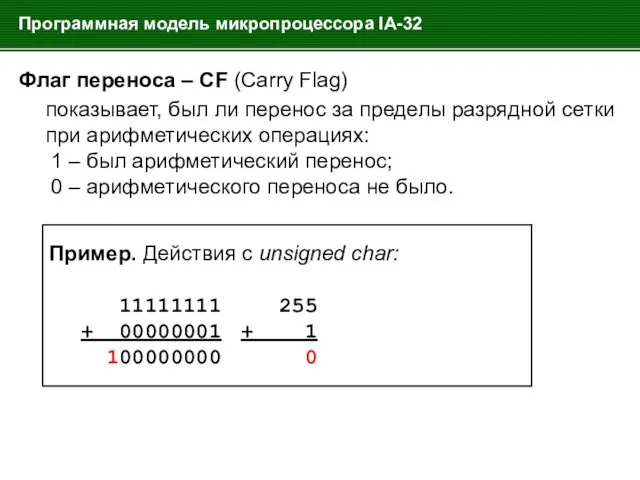

- 23. Программная модель микропроцессора IA-32 Флаг переноса – CF (Carry Flag) показывает, был ли перенос за пределы

- 24. Программная модель микропроцессора IA-32 сегмент смещение

- 25. Программная модель микропроцессора IA-32 Основные режимы работы процессора: – реальный режим; – защищенный режим; – режим

- 26. Программная модель микропроцессора IA-32 Реальный режим (режим реальных адресов) – соответствует режиму работы процессора Intel 8086

- 27. Программная модель микропроцессора IA-32 Вычисление адреса в реальном режиме адрес = сегмент*16 + смещение Поскольку величины

- 28. Программная модель микропроцессора IA-32 Величина сегмент берется из соответствующего сегментного регистра (код – CS, стек –

- 29. Программная модель микропроцессора IA-32 Недостатки механизма сегментации реального режима: – ограниченный максимальный размер сегмента (64 Кб);

- 30. Программная модель микропроцессора IA-32 Защищенный режим – реализован в процессорах, начиная с i80286 (1982 год); –

- 31. Программная модель микропроцессора IA-32 В защищенном режиме прямой доступ к физической памяти возможен только для программ,

- 32. Программная модель микропроцессора IA-32 Вычисление адреса в защищенном режиме – сегментный регистр содержит селектор – указатель

- 33. Программная модель микропроцессора IA-32 Преимущества сегментации памяти защищенного режима – большие размеры сегментов (до 4 Гб);

- 35. Скачать презентацию

Операційні системи. Керування оперативною пам'яттю. (Лекція 7)

Операційні системи. Керування оперативною пам'яттю. (Лекція 7) Файлы и файловые структуры. Компьютер как унивесальное устройство для работы с информацией. Информатика. 7 класс

Файлы и файловые структуры. Компьютер как унивесальное устройство для работы с информацией. Информатика. 7 класс Структуры данных

Структуры данных Двумерные массивы

Двумерные массивы Advanced Concepts and Long Term Vision

Advanced Concepts and Long Term Vision Кодирование и обработка графической информации

Кодирование и обработка графической информации Реализация бинарных деревьев на Си

Реализация бинарных деревьев на Си New CCC user guide 2017.5. Overseas Service Planning Team

New CCC user guide 2017.5. Overseas Service Planning Team МЗЯ1_2024 от 14.02.2024

МЗЯ1_2024 от 14.02.2024 Интеллектуальные информационные системы (ИИС). Лекция 3. Логическая модель представления знаний

Интеллектуальные информационные системы (ИИС). Лекция 3. Логическая модель представления знаний Формы мышления. Алгебра высказываний

Формы мышления. Алгебра высказываний Программирование (Python) (§17-22). 8 класс

Программирование (Python) (§17-22). 8 класс Алгоритмы размещения конструктивных модулей различных уровней иерархии

Алгоритмы размещения конструктивных модулей различных уровней иерархии Встраивание музыки в документы

Встраивание музыки в документы Компьютерные вирусы и антивирусные программы

Компьютерные вирусы и антивирусные программы Программирование на языке Си. Часть 1. Лексемы. Переменные. Константы. Основные операторы

Программирование на языке Си. Часть 1. Лексемы. Переменные. Константы. Основные операторы Создание базы адресов. Слияние

Создание базы адресов. Слияние Web, JSON

Web, JSON Теория программирования. Машина Тьюринга

Теория программирования. Машина Тьюринга Основы Информационной безопасности. (Безопасность экономической информации)

Основы Информационной безопасности. (Безопасность экономической информации) Flutter в действии

Flutter в действии Новая система электронного повышения квалификации учителей и руководителей образовательных организаций Московской области

Новая система электронного повышения квалификации учителей и руководителей образовательных организаций Московской области Аппаратное обеспечение компьютера hardware

Аппаратное обеспечение компьютера hardware Предмет и содержание курса. Алгоритмизация задач и программирование

Предмет и содержание курса. Алгоритмизация задач и программирование Структура сайта школьного музея

Структура сайта школьного музея Первая пара. Динамическое пр-е и рекурсия

Первая пара. Динамическое пр-е и рекурсия Операційна система Windows

Операційна система Windows Проектная работа ученика Исследование гармонических колебаний

Проектная работа ученика Исследование гармонических колебаний