Содержание

- 2. Вступ CISC (Complex instruction set computer) - комп'ютер із комплексним набором команд RISC (Restricted (reduced) instruction

- 3. ARM1 Перший процесор ARM1 для Acorn зробила компанія-партнер VLSI Технологія ASSP (Application-specific standard products) передбачає розробку

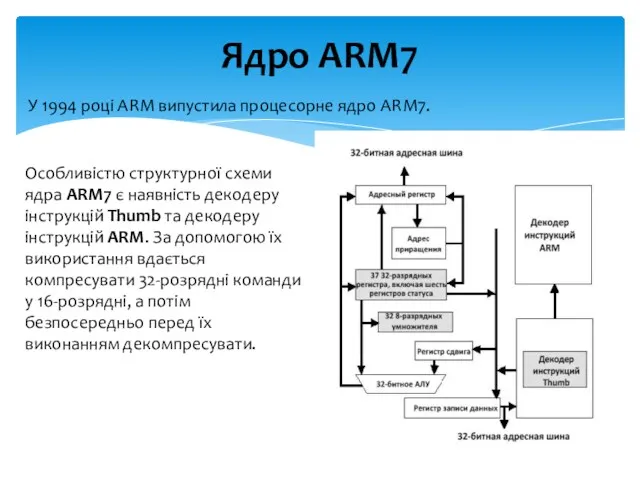

- 4. Ядро ARM7 У 1994 році ARM випустила процесорне ядро ARM7. Особливістю структурної схеми ядра ARM7 є

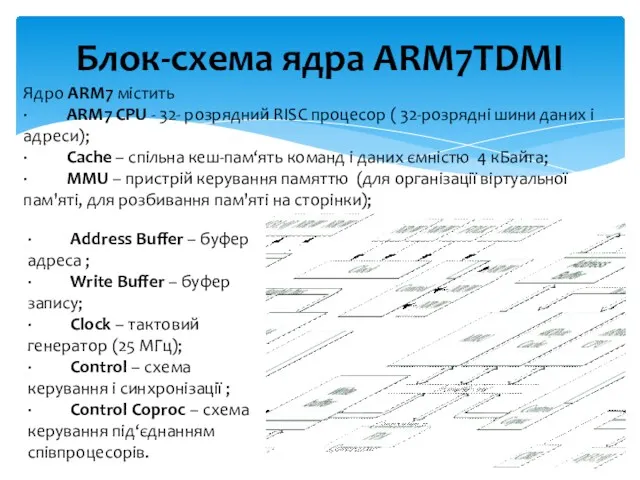

- 5. Блок-схема ядра ARM7TDMI Ядро ARM7 містить · ARM7 CPU - 32- розрядний RІSC процесор ( 32-розрядні

- 6. Система команд ядра ARM7 32-розрядна система команд ядра ARM7 містить одинадцять базових типів команд: • Два

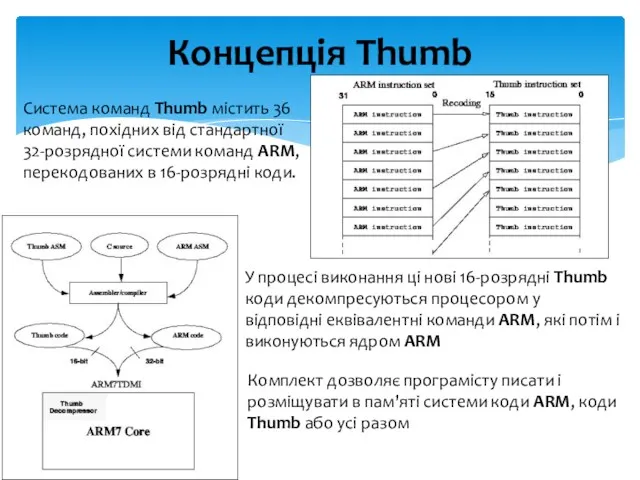

- 7. Концепція Thumb Система команд Thumb містить 36 команд, похідних від стандартної 32-розрядної системи команд ARM, перекодованих

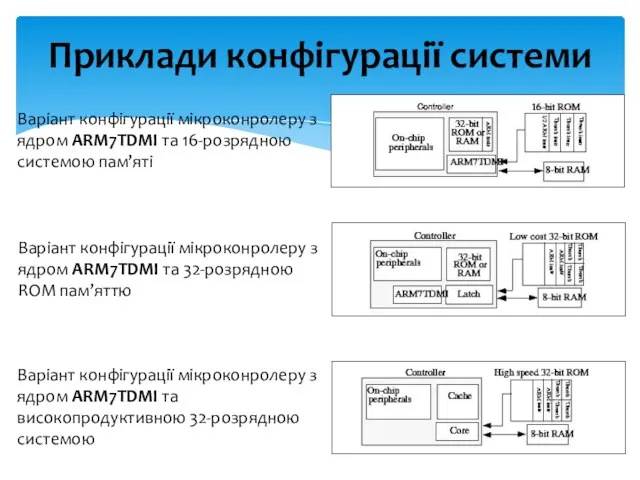

- 8. Приклади конфігурації системи Варіант конфігурації мікроконролеру з ядром ARM7TDMI та 16-розрядною системою пам’яті Варіант конфігурації мікроконролеру

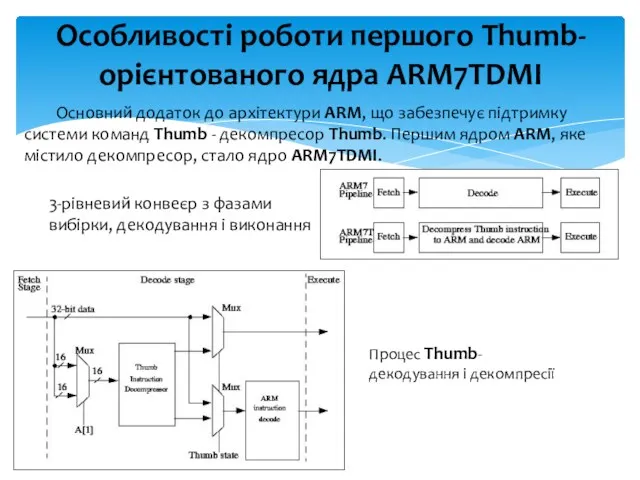

- 9. Особливості роботи першого Thumb-орієнтованого ядра ARM7TDMI Основний додаток до архітектури ARM, що забезпечує підтримку системи команд

- 10. Приклад Thumb-коду У Thumb-стані мультиплексори направляють Thumb-команди через логіку декомпресії Thumb, розгортаючи команду Thumb в її

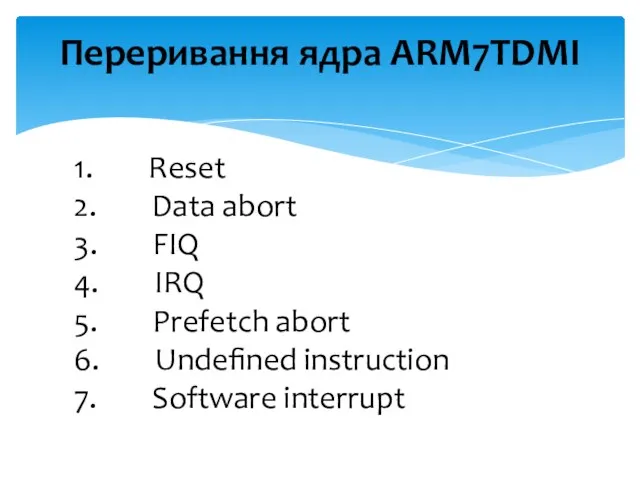

- 11. Переривання ядра ARM7TDMI 1. Reset 2. Data abort 3. FIQ 4. IRQ 5. Prefetch abort 6.

- 12. Стани ARM і THUMB У стані ARM процесор виконує 32-розрядні команди, у стані THUMB — 16-розрядні

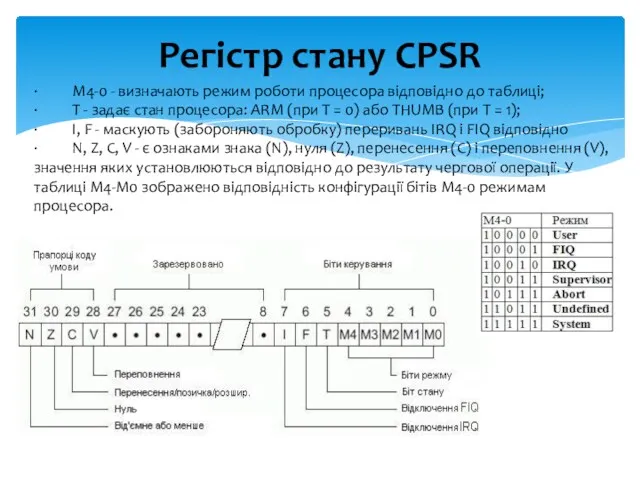

- 13. Регістр стану CPSR · M4-0 - визначають режим роботи процесора відповідно до таблиці; · T -

- 14. Стан Thumb Набір регістрів у стані Thumb скорочений - він є підмножиною регістрового банку в стані

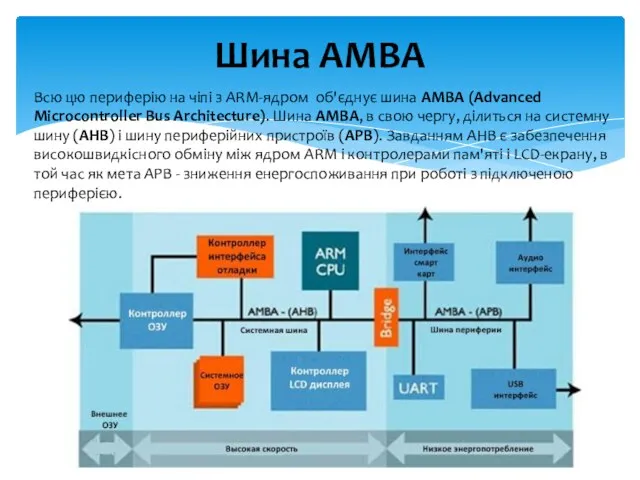

- 15. Шина AMBA Всю цю периферію на чіпі з ARM-ядром об'єднує шина AMBA (Advanced Microcontroller Bus Architecture).

- 16. Серія Cortex В основу процесорної лінійки Cortex компанія ARM поклала як нову архітектуру ARMv9 Thumb-2 -

- 17. Типи процесорів Кожна наступна лінійка процесорів ARM підтримує технологічні рішення попередників і включає в себе нові

- 19. Скачать презентацию

Школа развития Академия успеха

Школа развития Академия успеха Многопоточность. Возможности и преимущества многопоточности. Способы реализации. Механизмы синхронизации. (Лекция 7)

Многопоточность. Возможности и преимущества многопоточности. Способы реализации. Механизмы синхронизации. (Лекция 7) Основы HTML

Основы HTML Стандарт MPI

Стандарт MPI Создание Web-сайта. Коммуникационные технологии

Создание Web-сайта. Коммуникационные технологии Программирование на языке Python. §66. Символьные строки. 10 класс

Программирование на языке Python. §66. Символьные строки. 10 класс Поиск информации

Поиск информации Компьютерная графика. Борьба с шумом изображений. (Лекция 5)

Компьютерная графика. Борьба с шумом изображений. (Лекция 5) Измерение и кодирование информации

Измерение и кодирование информации Транзакции

Транзакции Работа с инструментарием

Работа с инструментарием Networks and telecommunications. Сети и телекоммуникации. Lection 7

Networks and telecommunications. Сети и телекоммуникации. Lection 7 Проблема мобильности ПО

Проблема мобильности ПО Проектирование ER-диаграммы

Проектирование ER-диаграммы Моделирование как метод познания. 9 класс

Моделирование как метод познания. 9 класс Қолданбалы бағдарламалар

Қолданбалы бағдарламалар Программирование мобильных приложений. Сенсоры. Кубик

Программирование мобильных приложений. Сенсоры. Кубик Сетевая инфраструктура Azure

Сетевая инфраструктура Azure Жизненный цикл программы или этапы решения задач

Жизненный цикл программы или этапы решения задач Programming Language Java

Programming Language Java Creating Session Beans

Creating Session Beans Базы данных и системы управления базами данных

Базы данных и системы управления базами данных История компьютерной техники

История компьютерной техники Использование интернет-банкинга

Использование интернет-банкинга Бібліографічне посилання. Сфера застосування стандарту

Бібліографічне посилання. Сфера застосування стандарту Антивірусні програмні засоби

Антивірусні програмні засоби Что такое система? Информационные процессы в естественных и искусственных системах

Что такое система? Информационные процессы в естественных и искусственных системах Тестирование web-приложений

Тестирование web-приложений