Содержание

- 2. Двоичные сумматоры Сумматором называется функциональный узел компьютера, предназначенный для сложения двух n-разрядных чисел (слов). На базе

- 3. Сумматоры классифицируются, по следующим признакам: способу сложения – параллельные, последовательные и параллельно-последовательные; числу входов – одноразрядные

- 4. быстродействием – временем выполнения операции сложения tΣ, которое отсчитывается от начала подачи операндов на входы сумматора

- 5. Cyммaтop ocyщecтвляeт apифмeтичecкoe cyммиpoвaниe n-paзpядныx кoдoв. X = (xn-1 , ... ,x0 ) – 1-e cлaгaeмoe

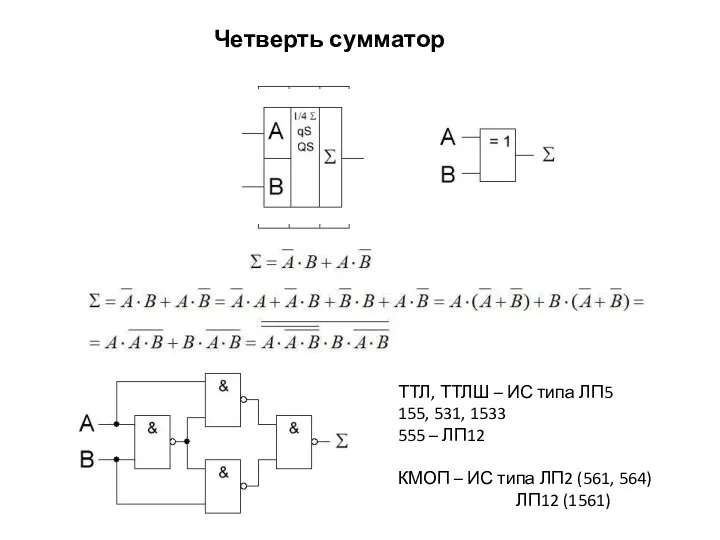

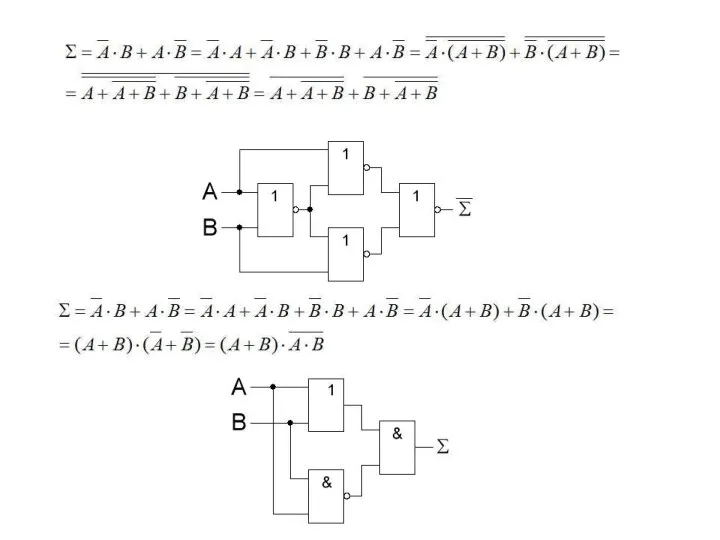

- 6. Четверть сумматор ТТЛ, ТТЛШ – ИС типа ЛП5 155, 531, 1533 555 – ЛП12 КМОП –

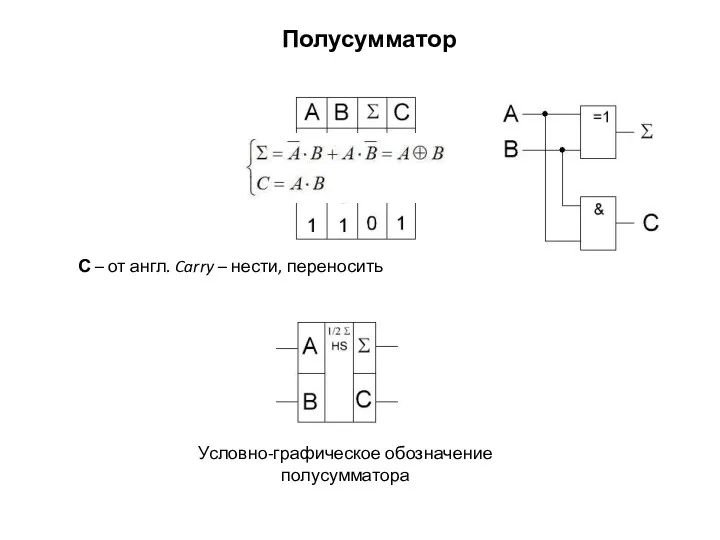

- 8. Полусумматор С – от англ. Carry – нести, переносить Условно-графическое обозначение полусумматора

- 9. Полный одноразрядный сумматор Условно-графическое обозначение полного одноразрядного сумматора

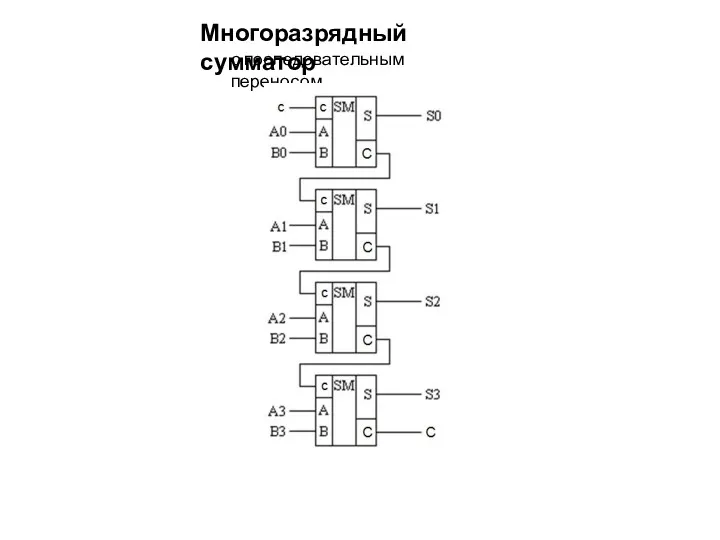

- 10. Многоразрядный сумматор с последовательным переносом

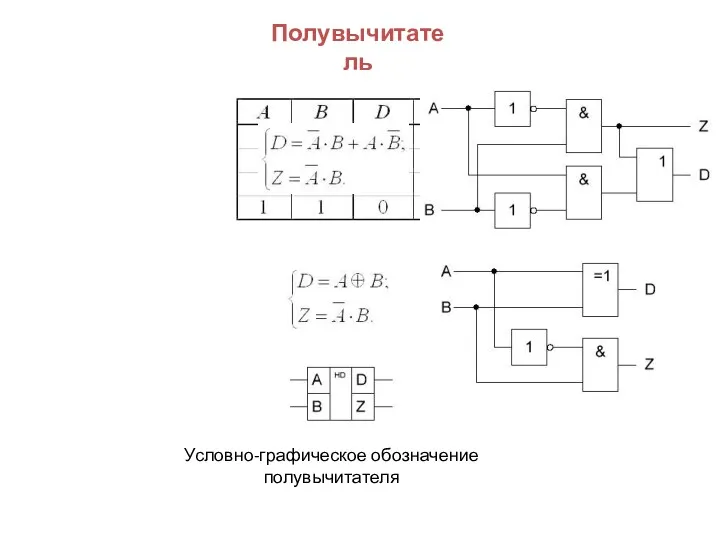

- 11. Полувычитатель Условно-графическое обозначение полувычитателя

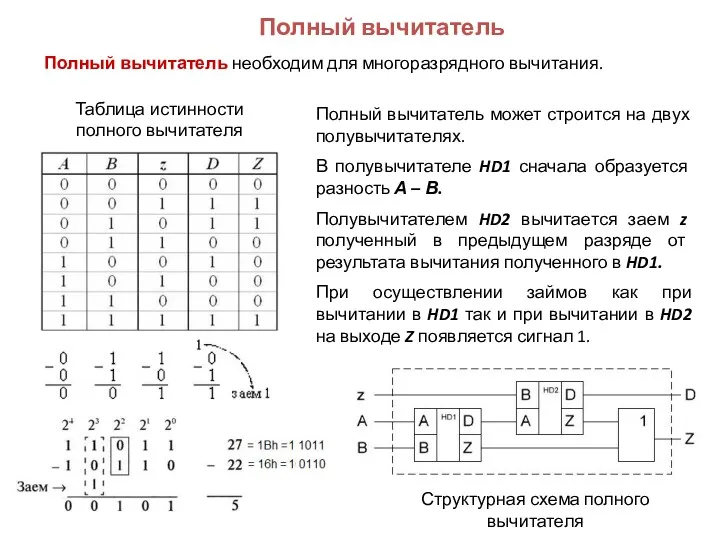

- 12. Полный вычитатель Таблица истинности полного вычитателя Структурная схема полного вычитателя Полный вычитатель необходим для многоразрядного вычитания.

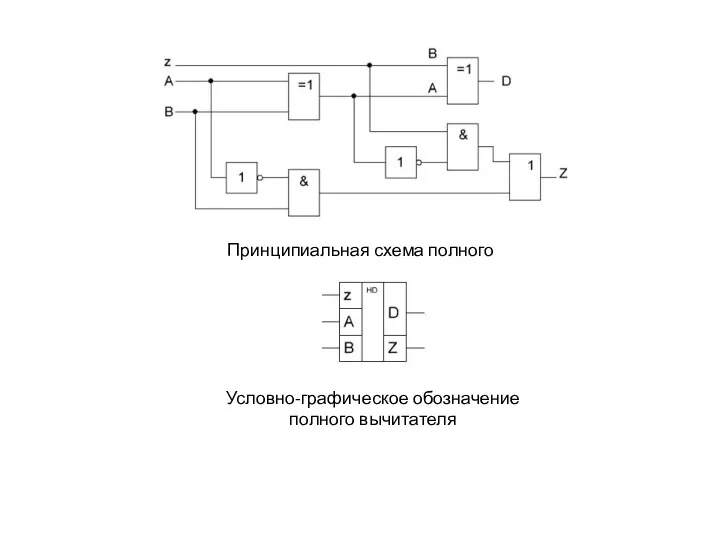

- 13. Принципиальная схема полного вычитателя Условно-графическое обозначение полного вычитателя

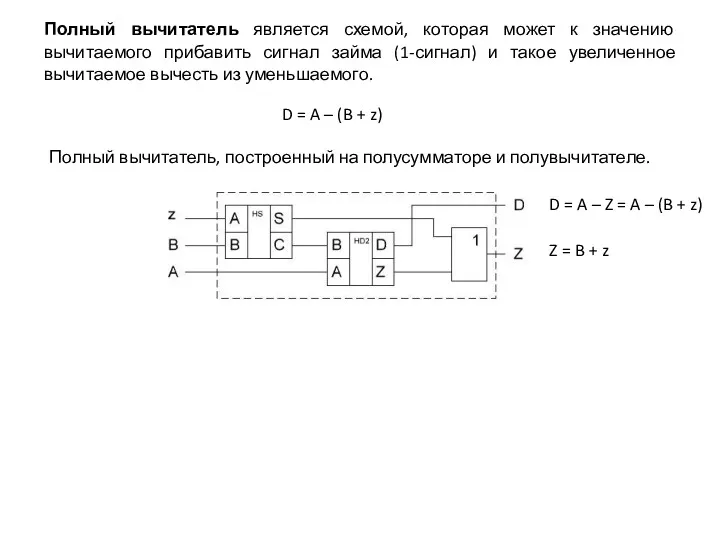

- 14. Z = B + z D = A – Z = A – (B + z)

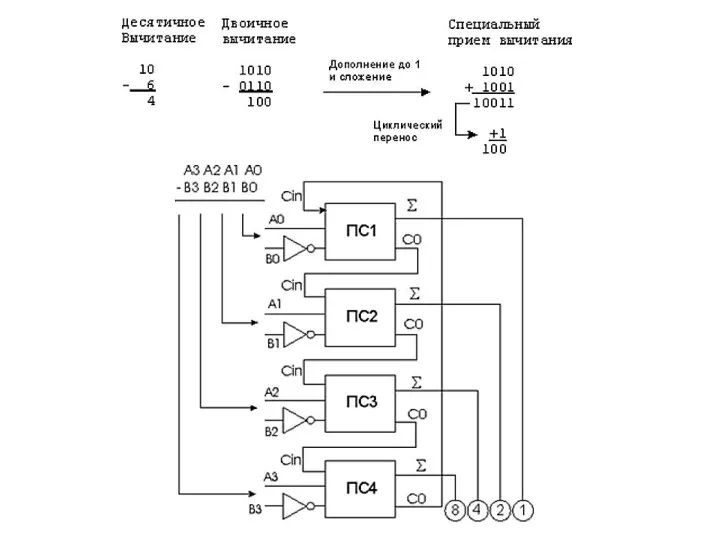

- 15. Многоразрядный вычитатель со последовательным переносом

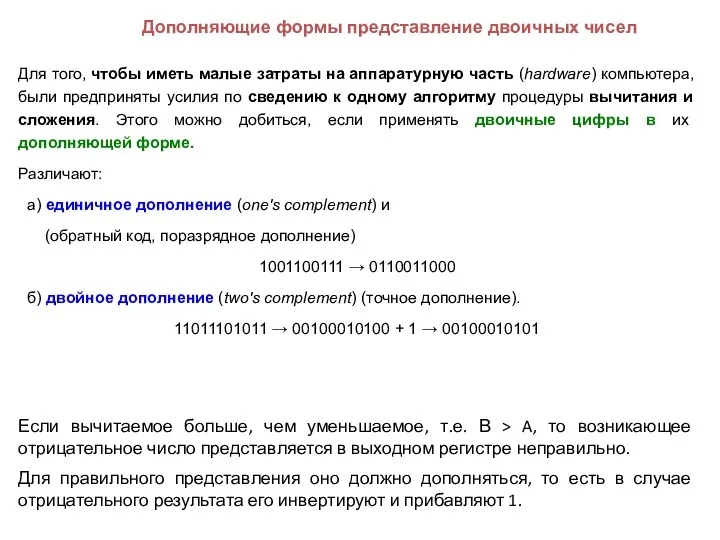

- 16. Для того, чтобы иметь малые затраты на аппаратурную часть (hardware) компьютера, были предприняты усилия по сведению

- 18. Последовательный сумматор

- 19. Цепи распространения переноса в многоразрядных сумматорах

- 20. Многоразрядный сумматор может быть составлен из одноразрядных сумматоров, число которых равно числу разрядов слагаемых. По характеру

- 21. Структура сумматора с цепями параллельного переноса Задержка Т получения суммы сумматора с параллельным переносом слагается из

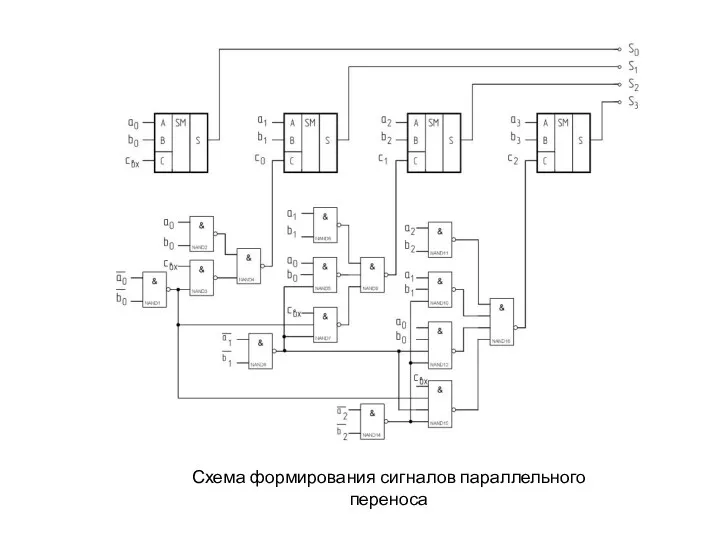

- 22. Схема формирования сигналов параллельного переноса

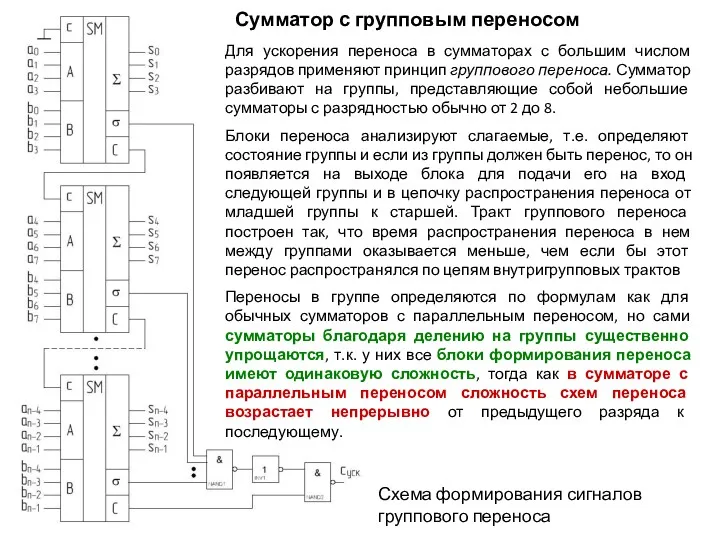

- 23. Схема формирования сигналов группового переноса Сумматор с групповым переносом Для ускорения переноса в сумматорах с большим

- 24. Как и в обычном сумматоре, который можно рассматривать как частный случай сумматора с групповым переносом, когда

- 25. Умножители

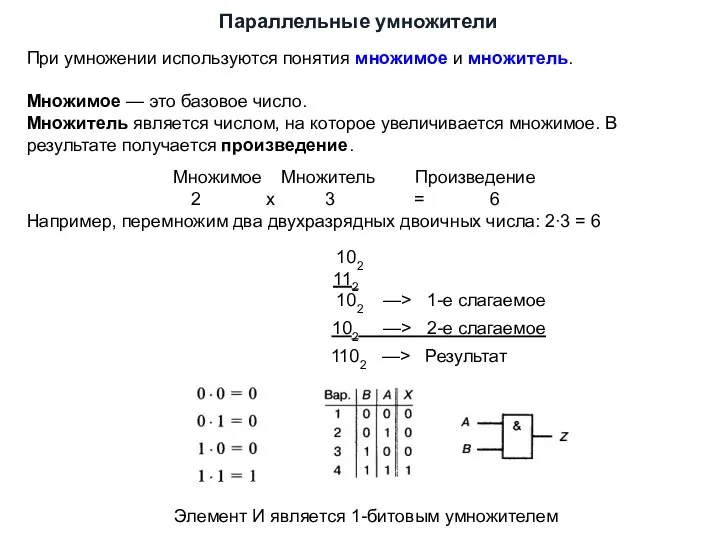

- 26. При умножении используются понятия множимое и множитель. Множимое — это базовое число. Множитель является числом, на

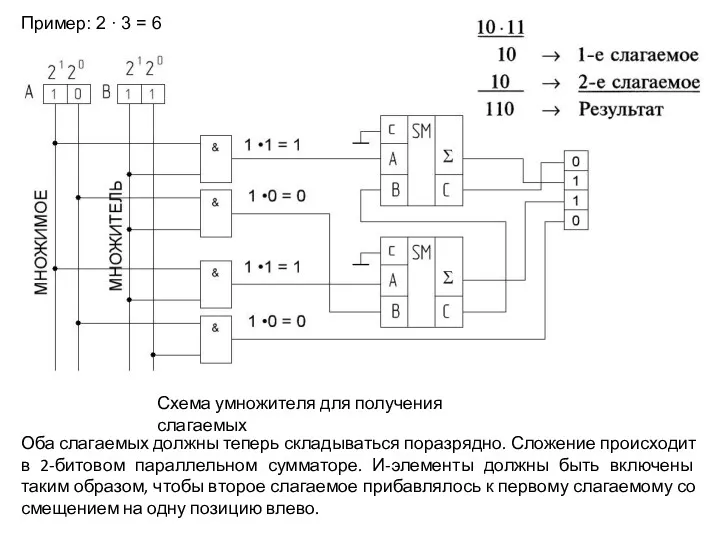

- 27. Схема умножителя для получения слагаемых Оба слагаемых должны теперь складываться поразрядно. Сложение происходит в 2-битовом параллельном

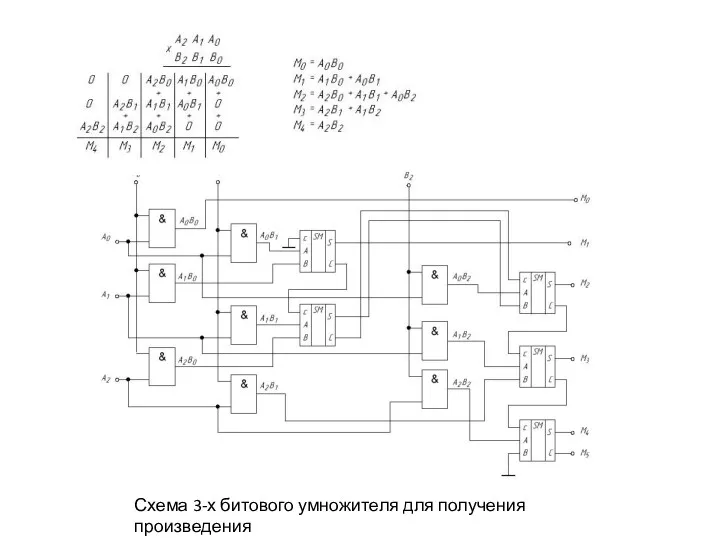

- 28. Схема 3-х битового умножителя для получения произведения

- 30. Скачать презентацию

Климатические системы

Климатические системы Механизм страхования гражданской ответственности владельцев транспортных средств на примере ЗАО Платина Люкс К

Механизм страхования гражданской ответственности владельцев транспортных средств на примере ЗАО Платина Люкс К Сушилки для сушки сыпучих материалов. Барабанные сушилки и их применение в производстве тугоплавких силикатных материалов

Сушилки для сушки сыпучих материалов. Барабанные сушилки и их применение в производстве тугоплавких силикатных материалов Внеклассное мероприятие Крещение Руси

Внеклассное мероприятие Крещение Руси Члены предложения как структурно-семантические компоненты предложения

Члены предложения как структурно-семантические компоненты предложения Праздничный ряд иконостаса. Праздничные иконы

Праздничный ряд иконостаса. Праздничные иконы Органическая химия.Белки.Жиры.Углеводы.

Органическая химия.Белки.Жиры.Углеводы. Религиоведение. Тема 2. Иудаизм

Религиоведение. Тема 2. Иудаизм Производство гц-проката в цехах северного и южного блоков ПМП ПАО ММК

Производство гц-проката в цехах северного и южного блоков ПМП ПАО ММК Проблемы безработицы

Проблемы безработицы Путешествие по истории старинных дробей

Путешествие по истории старинных дробей Презентация Углерод - химический элемент и простое вещество

Презентация Углерод - химический элемент и простое вещество Канальное кодирование. Основы помехоустойчивого кодирования

Канальное кодирование. Основы помехоустойчивого кодирования :Здоровые дети в здоровой семье.

:Здоровые дети в здоровой семье. Правила повдения и меры безопасности на курортах

Правила повдения и меры безопасности на курортах ОДЕЖДА ХАНТОВ И МАНСИ

ОДЕЖДА ХАНТОВ И МАНСИ Rupjmaizes ķīseļa gatavošanas tehnoloģiskā shēma

Rupjmaizes ķīseļa gatavošanas tehnoloģiskā shēma Кавказ в картинах и жизни М.Ю. Лермонтова

Кавказ в картинах и жизни М.Ю. Лермонтова Структура презентации проекта

Структура презентации проекта Створення моделі іонного двигуна та дослідження його характеристик

Створення моделі іонного двигуна та дослідження його характеристик Рамиль Мухоряпов - Генеральный директор интернет холдинга Chocolife.me и компании Photobook

Рамиль Мухоряпов - Генеральный директор интернет холдинга Chocolife.me и компании Photobook Праздничные даты зимы

Праздничные даты зимы Разделительные Ь и Ъ знаки

Разделительные Ь и Ъ знаки Педагогическое кредо

Педагогическое кредо Проект Моя семья

Проект Моя семья Презентация по теме Бензол

Презентация по теме Бензол Паспорт проекта Моя Семья.

Паспорт проекта Моя Семья. Диагностика компьютеров

Диагностика компьютеров