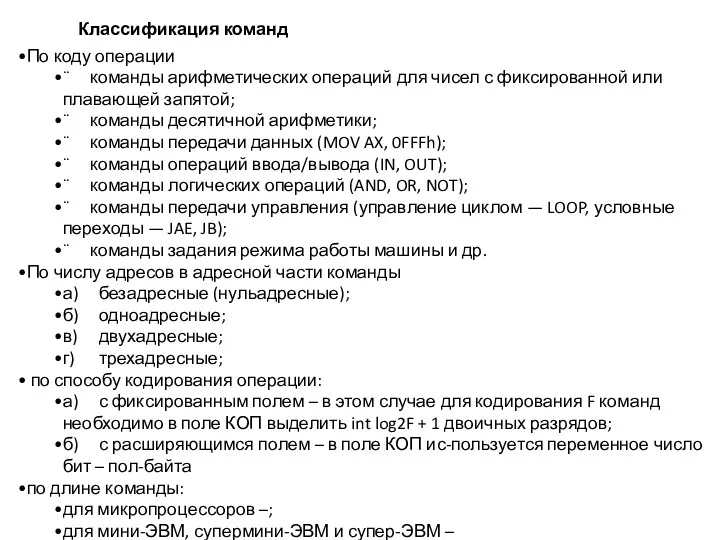

По коду операции

¨ команды арифметических операций для чисел с фиксированной или

плавающей запятой;

¨ команды десятичной арифметики;

¨ команды передачи данных (MOV AX, 0FFFh);

¨ команды операций ввода/вывода (IN, OUT);

¨ команды логических операций (AND, OR, NOT);

¨ команды передачи управления (управление циклом — LOOP, условные переходы — JAE, JB);

¨ команды задания режима работы машины и др.

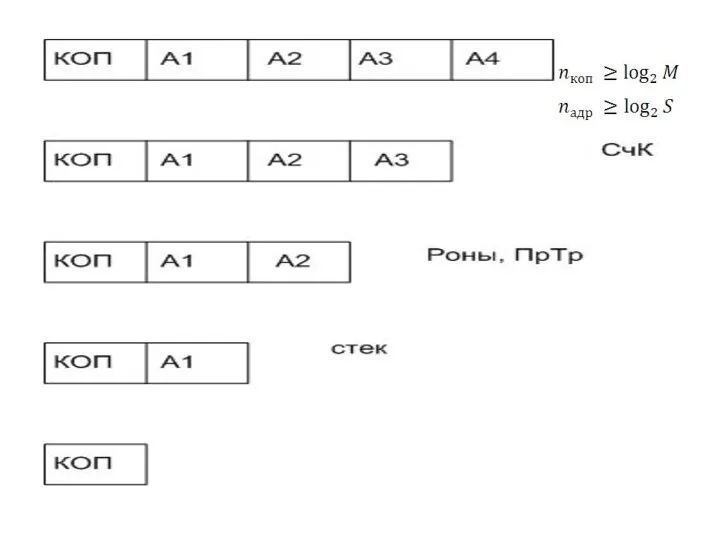

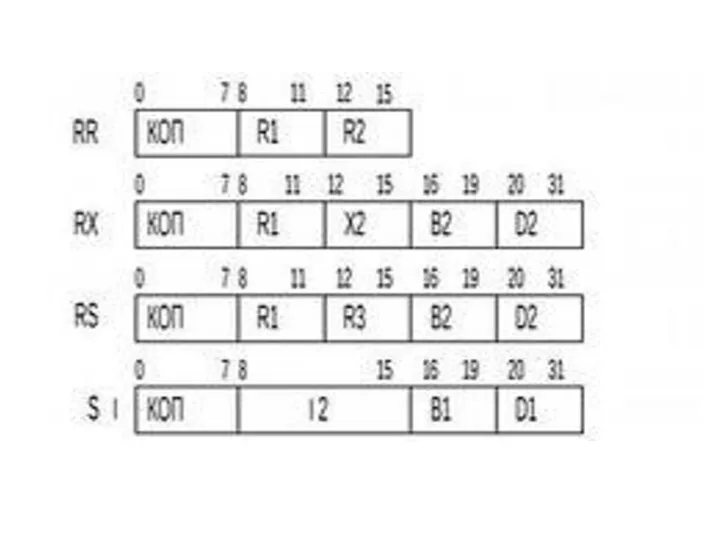

По числу адресов в адресной части команды

а) безадресные (нульадресные);

б) одноадресные;

в) двухадресные;

г) трехадресные;

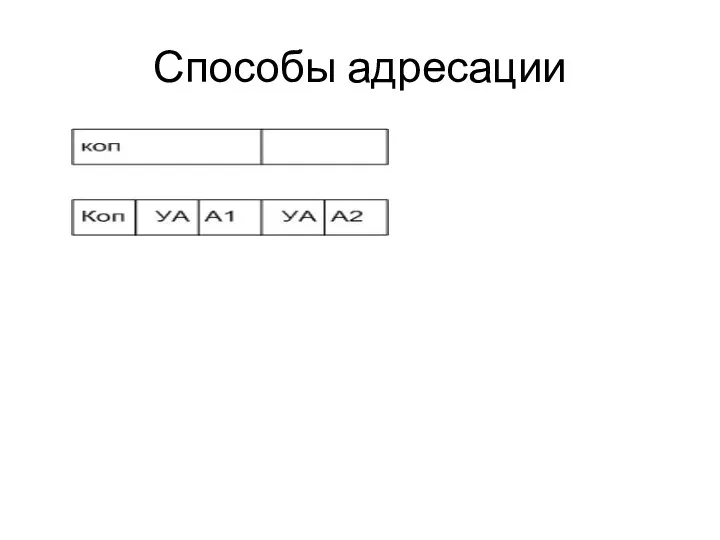

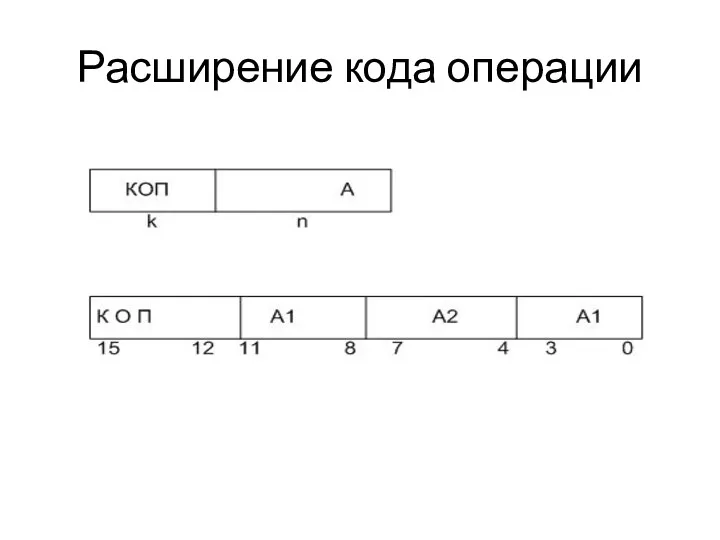

по способу кодирования операции:

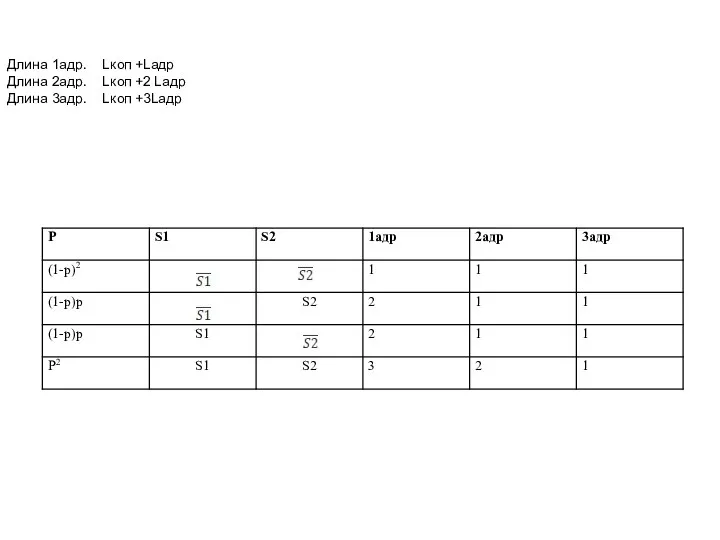

а) с фиксированным полем – в этом случае для кодирования F команд необходимо в поле КОП выделить int log2F + 1 двоичных разрядов;

б) с расширяющимся полем – в поле КОП ис-пользуется переменное число бит – пол-байта

по длине команды:

для микропроцессоров –;

для мини-ЭВМ, супермини-ЭВМ и супер-ЭВМ –

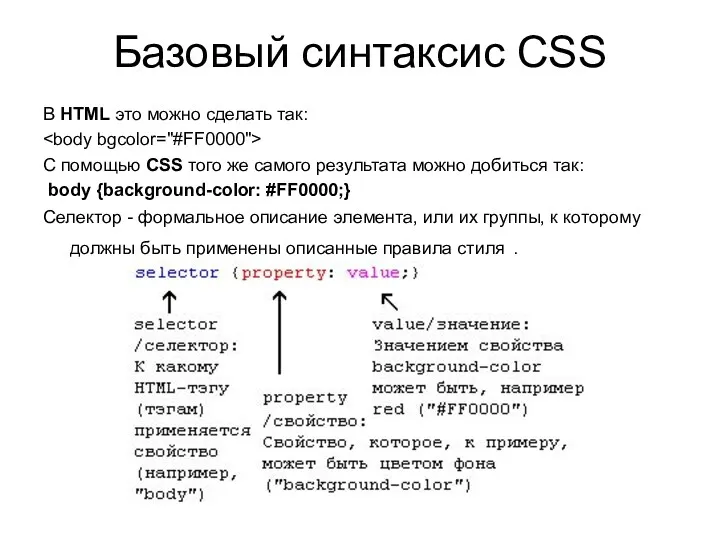

Классификация команд

![a=[101] [106,107]-вспомогательные ячейки b=[102] c=[103] d=[104] y=[105] 2000= CЛ 101,102,106, 2001 2001=Выч 103,104,107,2002 2002=Дел 106,107,105,2003](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/340680/slide-4.jpg)

Архитектура ОС MS Windows 2000+. Реестр

Архитектура ОС MS Windows 2000+. Реестр Электронные таблицы Excel

Электронные таблицы Excel История связи. Простейшие средства связи

История связи. Простейшие средства связи Растровая графика

Растровая графика مفاهيم دراسات المستفيدين من المعلومات

مفاهيم دراسات المستفيدين من المعلومات Компьютерные программные продукты для разработки бизнес-планов (Project Expert, COMFAR, Альт-Инвест, PROPSPIN)

Компьютерные программные продукты для разработки бизнес-планов (Project Expert, COMFAR, Альт-Инвест, PROPSPIN) Deep Web – теневой интернет

Deep Web – теневой интернет Программирование на Python

Программирование на Python Работа с диапазонами. Относительная адресация

Работа с диапазонами. Относительная адресация Определение количества информации

Определение количества информации Как создать компьютерный тест-пособие

Как создать компьютерный тест-пособие Система контроля устойчивости бортов. Преимущества выбора радаров MSR (reutech)

Система контроля устойчивости бортов. Преимущества выбора радаров MSR (reutech) Локальные компьютерные сети

Локальные компьютерные сети Создание базы адресов. Слияние

Создание базы адресов. Слияние Системы счисления

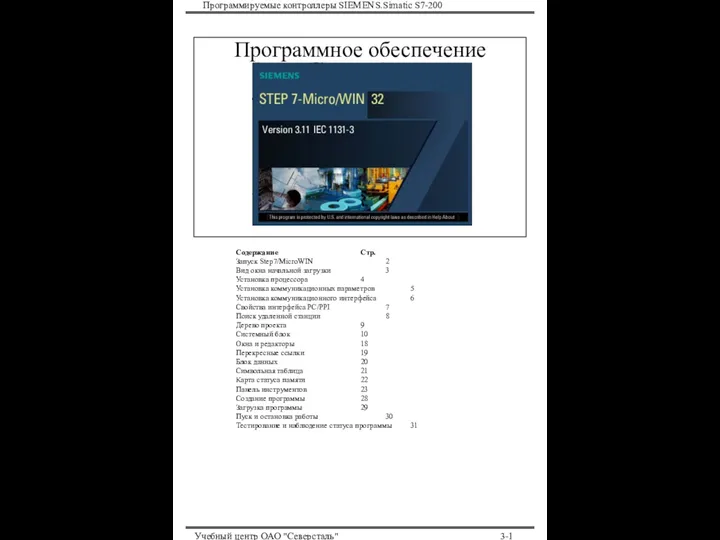

Системы счисления Программируемые контроллеры SIEMENS.Simatic S7-200. Программное обеспечение

Программируемые контроллеры SIEMENS.Simatic S7-200. Программное обеспечение Базовый синтаксис CSS в HTML

Базовый синтаксис CSS в HTML Возрастной рейтинг игр

Возрастной рейтинг игр Программирование на языке Python. §54. Алгоритм и его свойства

Программирование на языке Python. §54. Алгоритм и его свойства Составление индивидуальной траектории обучения

Составление индивидуальной траектории обучения Основы синтаксиса. Операции в PHP

Основы синтаксиса. Операции в PHP Администрирование информационных систем. Серверы имен. DNS, WINS

Администрирование информационных систем. Серверы имен. DNS, WINS Урок

Урок Правила безопасного поведения в интернете для детей и подростков

Правила безопасного поведения в интернете для детей и подростков Ручные операции Партнерского Прайса

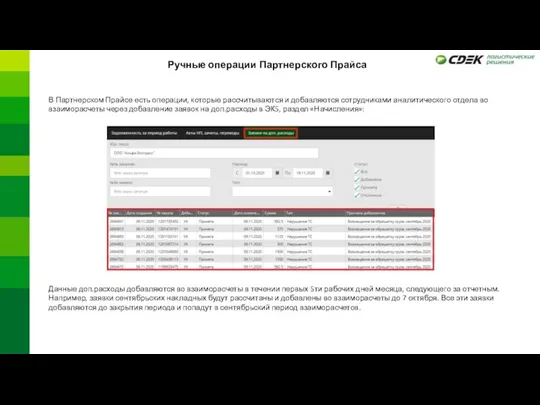

Ручные операции Партнерского Прайса Информационная культура. Основные понятия

Информационная культура. Основные понятия Урок по информатике в 9 классе на тему Мир электронной почты, телеконференция.

Урок по информатике в 9 классе на тему Мир электронной почты, телеконференция. Функції в Microsoft Excel

Функції в Microsoft Excel