Содержание

- 2. Для взаимодействия с различными модулями в ЭВМ должны быть средства идентификации ячеек внешней памяти, ячеек внутренней

- 3. Все способы адресации памяти можно разделить на: прямой, когда исполнительный адрес берется непосредственно из команды или

- 4. Двоичный n-разрядный номер ячейки памяти, к которой нужно обратиться в ходе выполнения вычислительного процесса, принадлежащий этой

- 5. Следует различать понятия исполнительный адрес и адресный код в формате команды. Исполнительный адрес — это номер

- 6. Команды разных микропроцессорных систем могут использовать различные способы адресации, которые применяются как сами по себе, так

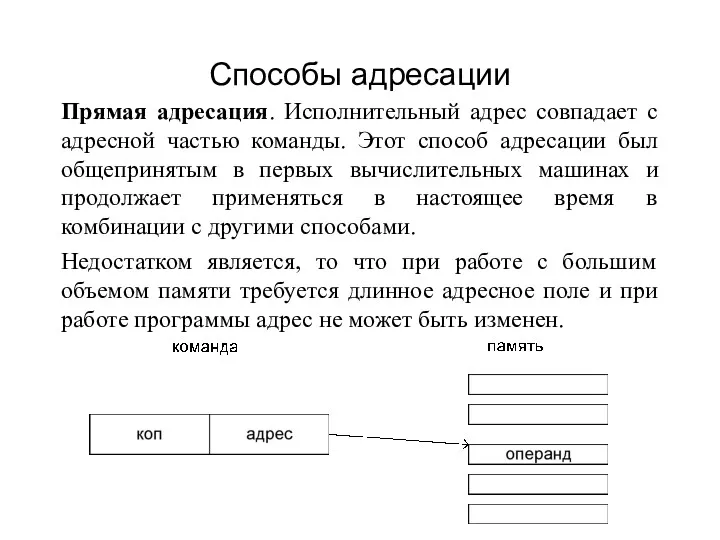

- 7. Способы адресации Прямая адресация. Исполнительный адрес совпадает с адресной частью команды. Этот способ адресации был общепринятым

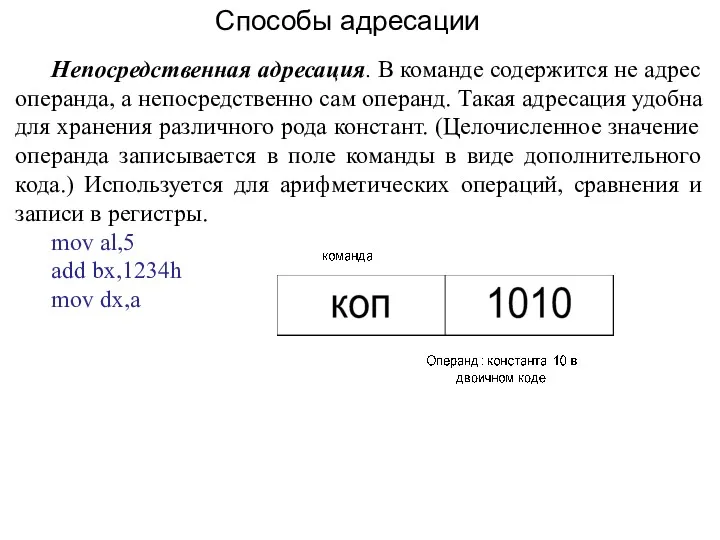

- 8. Непосредственная адресация. В команде содержится не адрес операнда, а непосредственно сам операнд. Такая адресация удобна для

- 9. Относительная адресация или базирование. Исполнительный адрес определяется суммой адресного кода команды АК и некоторого числа АБ

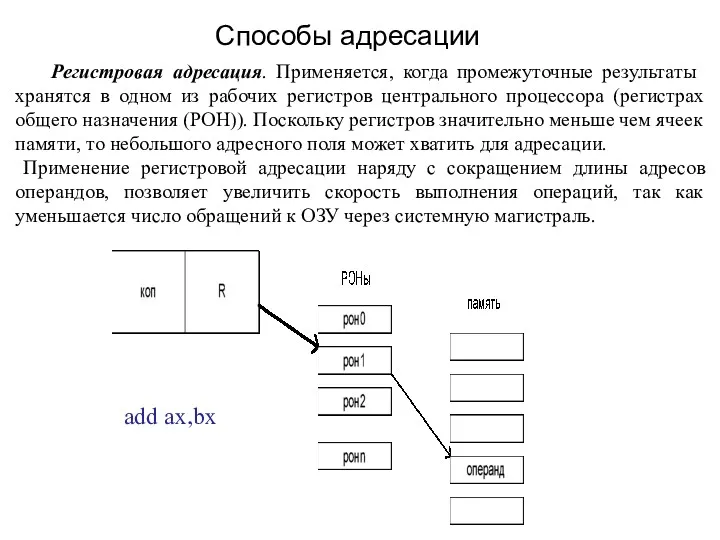

- 10. Регистровая адресация. Применяется, когда промежуточные результаты хранятся в одном из рабочих регистров центрального процессора (регистрах общего

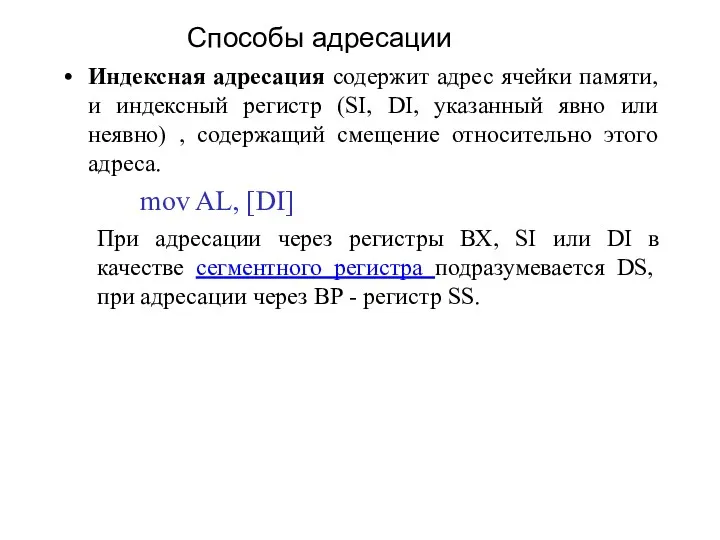

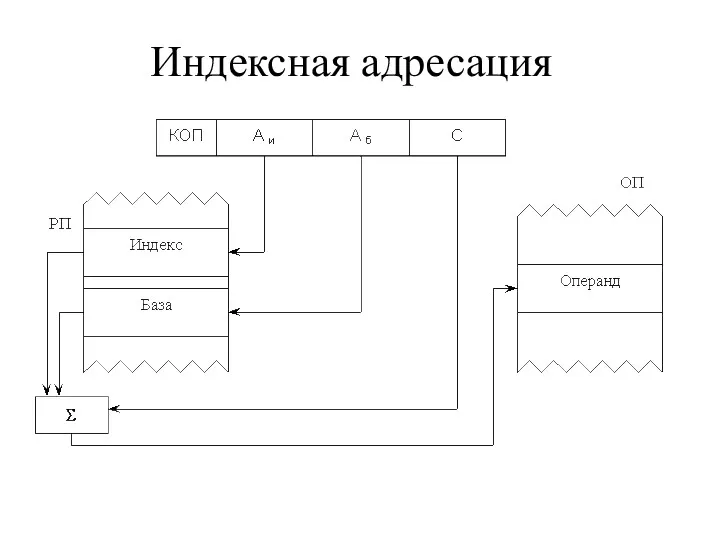

- 11. Индексная адресация содержит адрес ячейки памяти, и индексный регистр (SI, DI, указанный явно или неявно) ,

- 12. Индексная адресация

- 13. Сегментные регистры Всего шесть сегментных регистров: cs, ss, ds, es, gs, fs. Они предназначены для указания

- 14. 1. Сегмент кода. Содержит команды программы. Для доступа к этому сегменту служит регистр cs (code segment

- 15. 2. Сегмент данных. Содержит обрабатываемые программой данные. Для доступа к этому сегменту служит регистр ds (data

- 16. 3. Сегмент стека. Этот сегмент представляет собой область памяти, называемую стеком. Работу со стеком микропроцессор организует

- 17. 4. Дополнительный сегмент данных ds. Если программе недостаточно одного сегмента данных, то она имеет возможность использовать

- 18. Базово-индексная адресация памяти Относительный адрес операнда определяется суммой содержимого базового и индексного регистров. Допускается использование следующих

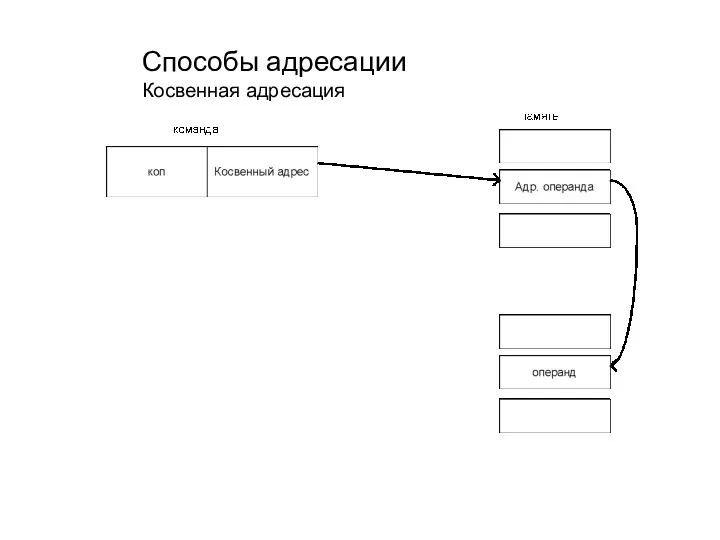

- 19. Косвенная адресация. Адресный код команды указывает адрес ячейки памяти, в которой находится адрес операнда или команды.

- 20. Способы адресации Косвенная адресация

- 21. Косвенная регистровая адресация - исполнительный адрес операнда хранится не в ячейке основной памяти, а в регистре

- 22. Косвенная базовая индексная адресация Адрес операнда вычисляется как сумма содержимого одного из базовых регистров BX или

- 23. Автоинкрементная и автодекрементная адресации. Обеспечивает эффективную работу с массивами данных, за счет формирования адреса следующего элемента

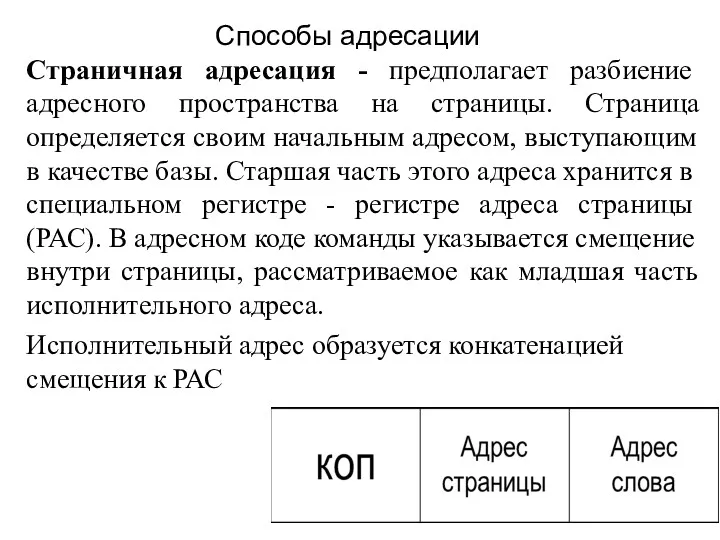

- 24. Страничная адресация - предполагает разбиение адресного пространства на страницы. Страница определяется своим начальным адресом, выступающим в

- 25. Стековая адресация Стек образует множество логически взаимосвязанных ячеек, взаимодействующих по принципу LIFO. Стековая память широко используется

- 26. Способы адресации

- 27. Для чтения и записи доступна только вершина стека. Этот способ адресации используется, в частности, системой прерывания

- 28. операнды перед обработкой помещаются в две верхних ячейки стековой памяти. Результат операции заносится в стек. Принцип

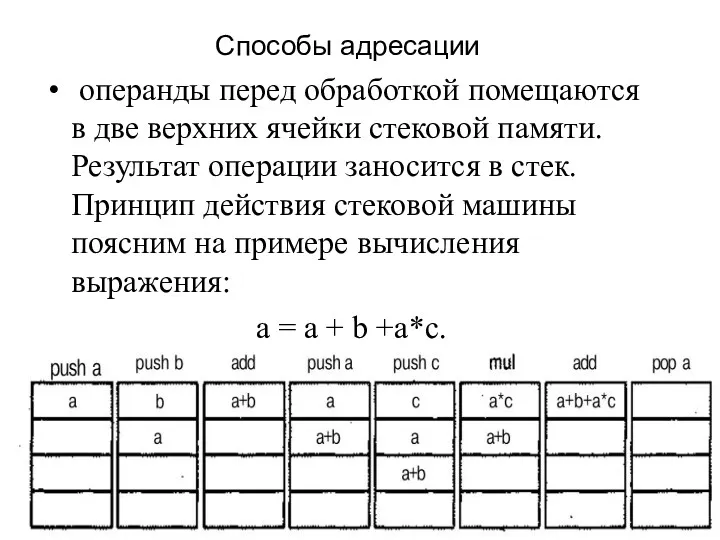

- 29. Использование всего набора способов адресации и их правильный выбор для каждого конкретного случая – позволяет: -

- 30. Форматы команд и способы адресации Обработка информации в микропроцессорной системе осуществляется автоматически, путем программного управления. Программа

- 32. Скачать презентацию

Способы несанкционированного доступа к информации и понятие аутентификации

Способы несанкционированного доступа к информации и понятие аутентификации Мое дело. Интернет-бухгалтерия

Мое дело. Интернет-бухгалтерия Использование функций в табличном процессоре MS EXCEL

Использование функций в табличном процессоре MS EXCEL Company Apple

Company Apple презентация Информационные технологии

презентация Информационные технологии San berlenleriň görnüşlerini özgertmek

San berlenleriň görnüşlerini özgertmek Программное обеспечение ПК

Программное обеспечение ПК Cloud Computing For Everyone. Module 2. Collaborating on Household Budgets

Cloud Computing For Everyone. Module 2. Collaborating on Household Budgets Delphi 3. Создание процедур на основе событий

Delphi 3. Создание процедур на основе событий Letters based on written input

Letters based on written input Представление информации в форме таблиц

Представление информации в форме таблиц Презентация к уроку Моделирование в программе QCAD

Презентация к уроку Моделирование в программе QCAD Безопасность общения в социальных сетях

Безопасность общения в социальных сетях Перевод между СС и представление чисел

Перевод между СС и представление чисел Уроки английского языка с умной колонкой-капсулой Маруся

Уроки английского языка с умной колонкой-капсулой Маруся Информационные оптимизационные модели. Оптимизация раскроя на языке программирования и в электронных таблицах

Информационные оптимизационные модели. Оптимизация раскроя на языке программирования и в электронных таблицах Доступное дополнительное образование для детей

Доступное дополнительное образование для детей Беспроводные сети. Спутниковая связь

Беспроводные сети. Спутниковая связь Язык программирования Pascal

Язык программирования Pascal Графика конструирование программ и языки программирования

Графика конструирование программ и языки программирования Информационное общество. Основы социальной информатики

Информационное общество. Основы социальной информатики Есептеуіш техниканың даму тарихы

Есептеуіш техниканың даму тарихы Контент-стратегии онлайн-СМИ

Контент-стратегии онлайн-СМИ Вычисления на GPU с использованием NVIDIA CUDA

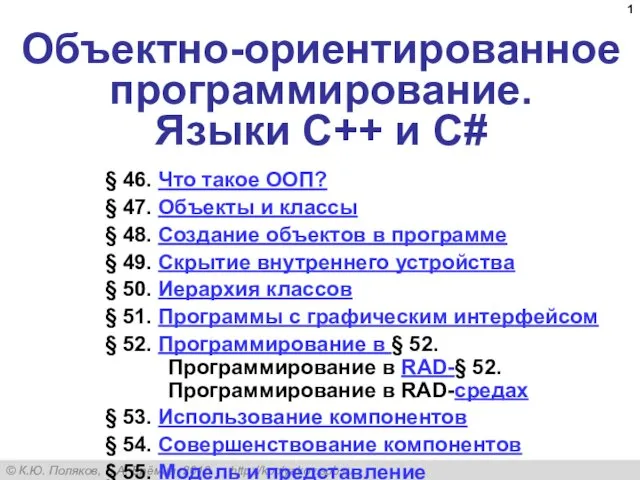

Вычисления на GPU с использованием NVIDIA CUDA Объектно-ориентированное программирование. Языки C++ и C#

Объектно-ориентированное программирование. Языки C++ и C# Методика проведения юзабилити-тестирования веб-сайта

Методика проведения юзабилити-тестирования веб-сайта Разработка информационной системы для контроля эффективности сотрудников

Разработка информационной системы для контроля эффективности сотрудников Работа с макетом сайта

Работа с макетом сайта