Понятие архитектуры ЭВМ. Принципы Дж. фон Неймана/ Основные архитектуры/ История развития архитектуры IA-32 презентация

Содержание

- 2. Архитектура ЭВМ Архитектурой компьютера называется его описание на некотором общем уровне, включающее описание пользовательских возможностей программирования,

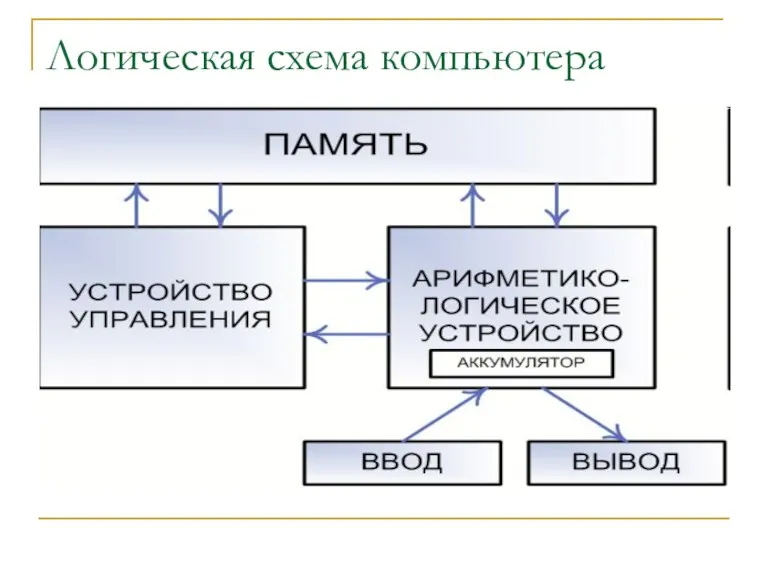

- 3. Логическая схема компьютера

- 4. Принципы Джона фон Неймана Принцип использования двоичной системы счисления для представления данных и команд. Принцип программного

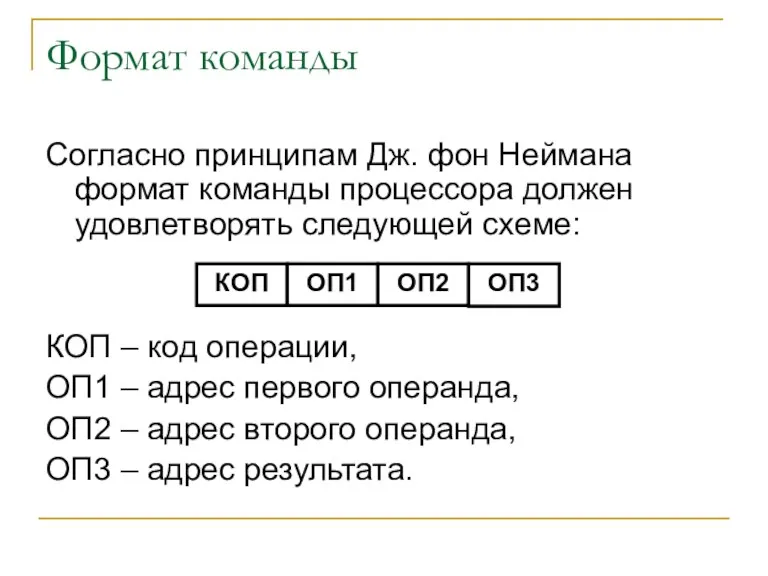

- 5. Формат команды Согласно принципам Дж. фон Неймана формат команды процессора должен удовлетворять следующей схеме: КОП –

- 6. Гарвардская архитектура Гарвардская архитектура была разработана в одно время с архитектурой Дж. фон Неймана, но начала

- 7. Современные архитектуры Все современные архитектуры компьютеров можно разделить на: CISC RISC VLIW

- 8. Архитектура CISC CISC (англ. Complex Instruction Set Computing) — концепция проектирования процессоров, которая характеризуется следующим набором

- 9. Архитектура RISC RISC (англ (англ. Reduced Instruction Set Computer) — компьютер с сокращённым набором команд. Особенности

- 10. Архитектура RISC Сопутствующие архитектуры: Суперскалярные архитектуры (первоначально Sun SPARC, начиная с Pentium использованы в семействе x86).

- 11. Архитектура RISC Иные архитектурные решения, типичные для RISC: Спекулятивное исполнение. При встрече с командой условного перехода

- 12. Архитектура VLIW VLIW (англ. Very long instruction word — «очень длинная машинная команда») — архитектура процессоров

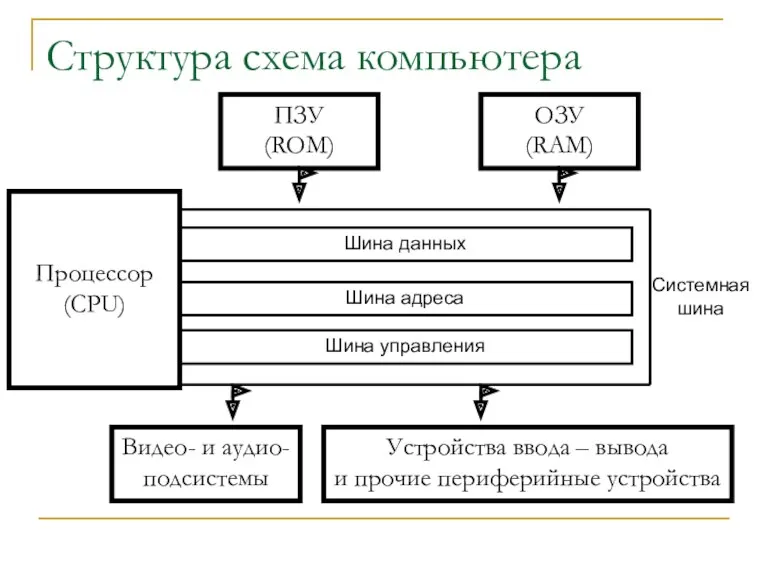

- 13. Структура схема компьютера Процессор (CPU) ПЗУ (ROM) ОЗУ (RAM) Устройства ввода – вывода и прочие периферийные

- 14. Архитектура IA-32 «Основоположники» семейства – процессоры 8086 и 8088 (1978 г.) Основные характеристики: 16 разрядные регистры,

- 15. Архитектура IA-32 Сегментация – разделение всей доступной памяти на отдельные блоки (сегменты), которые не могут перекрывать

- 16. Архитектура IA-32 Intel® 286 Processor (1982 г.) Основные нововведения: Защищенный режим работы. 24-разрядный адрес (максимальный объем

- 17. Архитектура IA-32 Intel386™ Processor (1985 г.) Основные нововведения: 32-х разрядные регистры общего назначения. 32-х разрядная шина

- 18. Архитектура IA-32 Intel486™ Processor (1989 г.) Основные нововведения: Конвейерная обработка команд (5-ти стадийный конвейер). Появление КЭШ-памяти.

- 19. Архитектура IA-32 Intel® Pentium® Processor (1993 г.) Основные нововведения: Появление второго конвейера. Разделение КЭШ-памяти на КЭШ-данных

- 20. Архитектура IA-32 The P6 Family of Processors (1995 – 1999 гг) Данное семейство представлено следующими процессорами:

- 21. Архитектура IA-32 Intel® Pentium® 4 Processor Family (2000 – 2006 гг) Основные нововведения: Появление SSE2, а

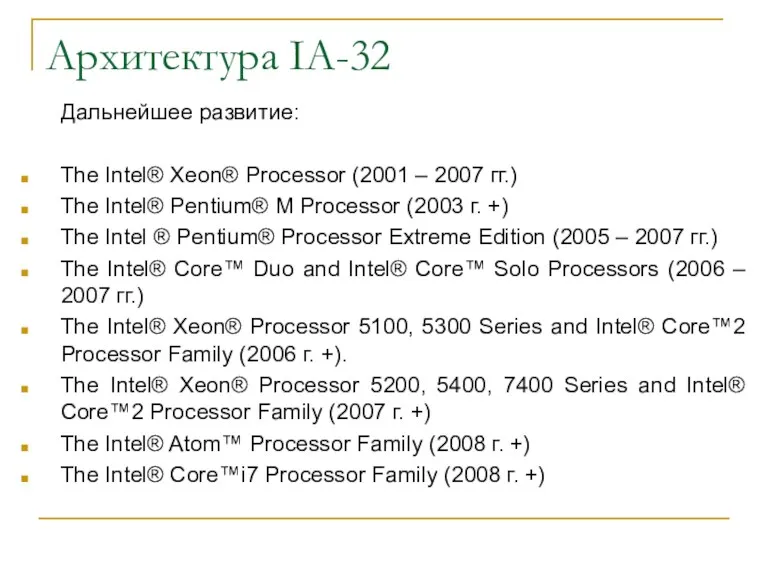

- 22. Архитектура IA-32 Дальнейшее развитие: The Intel® Xeon® Processor (2001 – 2007 гг.) The Intel® Pentium® M

- 24. Скачать презентацию

Практ.работа № 7

Практ.работа № 7 Диспансеризация населения: методология и современные подходы

Диспансеризация населения: методология и современные подходы портфолио

портфолио Конструктивные дефекты швейных изделий

Конструктивные дефекты швейных изделий Взаимные положения прямой и плоскости, двух плоскостей. (Лекция 5)

Взаимные положения прямой и плоскости, двух плоскостей. (Лекция 5) Урок ИКН в 7 классе Тема: Марийский край и губернские реформы XVIII века. Гербы городов

Урок ИКН в 7 классе Тема: Марийский край и губернские реформы XVIII века. Гербы городов Лайфхаки семейной жизни от современных психологов

Лайфхаки семейной жизни от современных психологов освобождение Воронежа

освобождение Воронежа Podstawy finansów. Rachunek wyników

Podstawy finansów. Rachunek wyników Электронная система зажигания

Электронная система зажигания Презентация во 2 классе на тему Моя семья

Презентация во 2 классе на тему Моя семья Однородные члены предложения. Пунктуация

Однородные члены предложения. Пунктуация Общая характеристика металлов IА группы ПСХЭ Д.И. Менделеева

Общая характеристика металлов IА группы ПСХЭ Д.И. Менделеева Интеграция образовательных областей по приобщению детей к народной мордовской игровой культуре

Интеграция образовательных областей по приобщению детей к народной мордовской игровой культуре Подготовка к выполнению части 2 ЕГЭ по обществознанию

Подготовка к выполнению части 2 ЕГЭ по обществознанию Разработки уроков

Разработки уроков Приливные электростанции

Приливные электростанции Спортивный комплекс Крылатское

Спортивный комплекс Крылатское Проект День Светлой Пасхи

Проект День Светлой Пасхи Проведение расчетов с бюджетом и внебюджетными фондами. Федеральное агентство по рыболовству БГАРФ ФГБОУ ВО КГТУ

Проведение расчетов с бюджетом и внебюджетными фондами. Федеральное агентство по рыболовству БГАРФ ФГБОУ ВО КГТУ Презентация Пушкарева Татьяна Павловна. Портфолио учителя

Презентация Пушкарева Татьяна Павловна. Портфолио учителя Презентация День Победы

Презентация День Победы Система NTSC

Система NTSC Комплексная автоматизация технологического процесса компании ООО Дионис

Комплексная автоматизация технологического процесса компании ООО Дионис Религиоведение. Предмет, цель и задачи курса

Религиоведение. Предмет, цель и задачи курса Етті өңдейтің өнеркәсіптердің маңызы және сою цехы

Етті өңдейтің өнеркәсіптердің маңызы және сою цехы Заполнители из природных плотных каменных пород

Заполнители из природных плотных каменных пород Культура эпохи Мэйдзи

Культура эпохи Мэйдзи